基于TMS320C6678 DSP的電源設(shè)計(jì)方案

UCD7242是與UCD9244完全兼容的驅(qū)動(dòng)芯片,可以驅(qū)動(dòng)兩個(gè)獨(dú)立的電源,可以供應(yīng)CVDD(內(nèi)核電壓)與VCC1V0(SRIO、PCIE、SGMII和Hyperlink)。通過(guò)1片9244控制兩片7242來(lái)達(dá)到為兩片DSP6678供電的目的。UCD7242電路中電感值的選擇很關(guān)鍵,根據(jù)芯片內(nèi)部結(jié)構(gòu),電感值的計(jì)算可以通過(guò)下面這個(gè)公式?jīng)Q定:

式中:VIN為輸入電壓,VOUT為輸出電壓,fs為工作頻率,D為占空比,△I為電感電流峰峰值。在本設(shè)計(jì)中,VIN=12 V,VOUT=1 V,D=1/12,fs=750 kHz,△I=10 A,可計(jì)算得電感,L≈0.122μH.

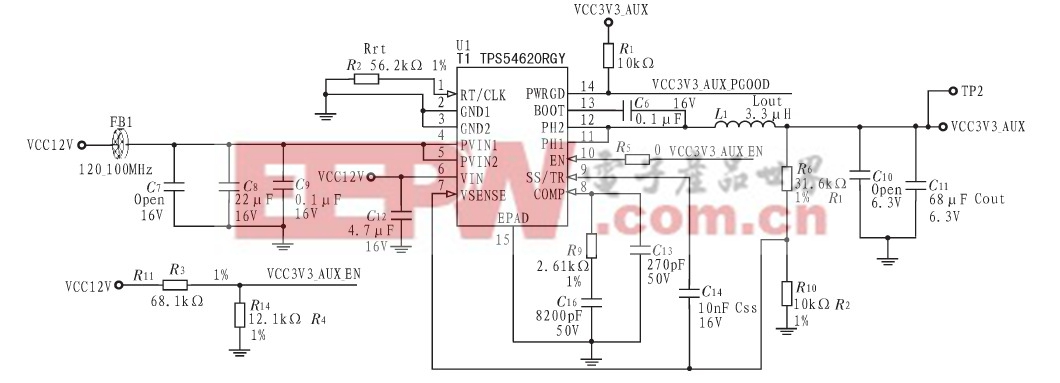

1.3 3.3 V輔助電源電路

在整體的系統(tǒng)中,有些芯片是需要3.3 V的工作電壓的,比如TPS73701,為DSP IO供電;TPS51200作為DDR3的參考電壓。圖3為采用TPS54620芯片作為電壓轉(zhuǎn)換芯片的電路,TPS54620的耐熱性能增強(qiáng),功能齊全,支持高效率,集成了高側(cè)/低側(cè)MOSFETs,并且輸出電壓可以調(diào)節(jié)。在本設(shè)計(jì)中,用TPS54620產(chǎn)生了3.3 V和1.5 V的電壓。如圖3所示,輸出電壓為:

式中:R10、R11為分壓電阻,Vref為參考電壓,經(jīng)實(shí)驗(yàn)設(shè)定R10=31.6 kΩ;R11=10 kΩ;Vref=0.8 V,可以得出輸出電壓VO=3.3 V。

圖3 3.3 V輔助電源電路

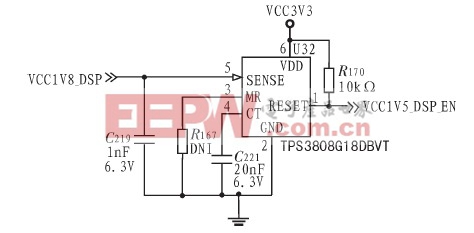

1.4 時(shí)序控制電路

該時(shí)序控制電路主要是用來(lái)控制6678DSP的IO、DDR3參考電壓以及HyperLink、PCIE等上電時(shí)序的。以DVDD18先于DDR3_IO上電為例,電路原理圖如圖4所示,所用的芯片為TPS3808G18,只有DVDD18=1.8 V時(shí),RESET才會(huì)輸出一個(gè)高電平,從而可以驅(qū)動(dòng)下一級(jí)電路,這樣就保證了時(shí)序要求,值得注意的是,延遲時(shí)間是可以控制的,通過(guò)控制CT引腳與地之間的電容值就可以實(shí)現(xiàn),參考公式為:

CT(nF)=[tD(s)-0.5x10-3(s)]×175 (3)

式中tD為設(shè)置的延遲時(shí)間。

圖4 時(shí)序控制

1.5 濾波網(wǎng)絡(luò)

在過(guò)去的DSP中,EMI濾波器(T型濾波器)用在那些易受噪聲影響的電源軌中,這些濾波器通常都是低通濾波器,這樣可以限制在每個(gè)相應(yīng)電源供應(yīng)的寄生耦合噪聲而不至于把直流分量濾除。其實(shí),在設(shè)計(jì)PCB板的時(shí)候,很多與DSP相關(guān)的問(wèn)題都是由于不注意EMI濾波器導(dǎo)致的。文中設(shè)計(jì)的濾波網(wǎng)絡(luò)主要是由旁路電容串聯(lián)磁珠,然后加上去耦電容組成的,這樣的設(shè)計(jì)在實(shí)際使用中效果很好。

評(píng)論