基于DDR3存儲器接口控制器IP核的視頻數據處理

與過去幾代(DDR和DDR2)器件相比,DDR3存儲器器件有了明顯的進步。DDR3存儲器系統可以大大提升各種數據處理應用的性能。為了充分利用和發揮DDR3存儲器的優點,使用一個高效且易于使用的DDR3存儲器接口控制器是非常重要的。視屏處理應用就是一個很好的示例,說明了DDR3存儲器系統的主要需求以及在類似數據流處理系統中DDR3接口所需的特性。希望能給大家有個客觀的認知。

視頻處理系統將對于數據帶寬的要求推高到了極致:系統可以處理越多的數據,就具有越高的性價比。視頻聚合器和路由器可并行處理多個視頻流,因此對于匹配數據處理能力和視頻帶寬的需求就成為了設計的一大挑戰。FPGA可通過在單個FPGA中實現多個視頻處理器來提供強大的處理能力。那么現在的挑戰就變成了要使數據盡快且高效地從FPGA進出。DDR3存儲器系統在大多數情況下可以為這些基于FPGA的系統提供足夠的帶寬。

視頻處理設計說明

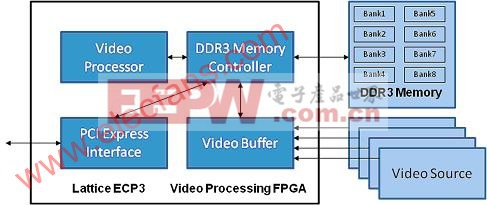

我們的目標視頻處理設計將同時處理四個視頻源,將視頻數據轉換和壓縮為一種可以通過PCI Express接口傳輸到存儲器hub的格式。系統的主要功能塊如圖1所示。

圖1:視頻處理器框圖

FPGA獲取并緩存四個視頻源的數據流。這些FIFO緩沖器由DDR3存儲器控制器清空并保存在DDR3存儲器中。一旦一個完整的視頻數據包存儲完畢,視頻處理器會向DDR3存儲器控制器申請數據,存儲器控制器讀取數據并將其傳到視頻處理器。視頻處理器對視頻數據進行格式化和壓縮,并通過DDR3存儲器控制器寫回存儲器。當一個視頻數據包全部處理完畢,并準備通過PCI Express接口進行傳輸,DDR3存儲器控制器從視頻處理器獲取數據并將其傳到PCI Express接口。

DDR3存儲器接口控制器概述

雙倍數據速率(DDR3)同步動態隨機存取存儲器(SDRAM)控制器是一種通用存儲器控制器,能與行業標準的DDR3 SDRAM器件和具有JESD79 - 3C型規范兼容的模塊接口。并對用戶應用提供了一個通用命令接口。DDR3 SDRAM是新一代SDRAM存儲器技術,具有更快的速度,緩沖SSO,由于直接將信號連到SDRAM,取代了低偏移的樹狀分布的方法,因此減少了布線。這個IP核減少了需要整合DDR3存儲器控制器與應用的其余部分所需投入的工作量。

特點

支持所有LatticeECP3“EA”器件

能與工業標準的DDR3 SDRAM器件和具有JESD79 - 3C規范兼容的模塊接口

高性能DDR3,高達400 MHz/800 Mbps的操作

支持存儲器數據路徑寬度為8 - ,16 - ,32和64位

支持x8和x16器件配置

支持無緩沖的DDR3 DIMM

支持一個DIMM和每個DIMM的一個級

8(固定)、“chopped 4”,或8(傳輸),或“chopped 4”(固定)的可編程突發長度

可編程的CAS延遲

可編程寫延遲

四位順序或交織的讀突發類型

支持自動的DDR3 SDRAM的初始化和刷新

對每個DQS自動寫

支持掉電模式

支持動態片上終端(ODT)的控制

終端數據選通(TDQS),僅適用x8寬度

ECP3 IO原語管理讀偏移(讀電平相等)

自動可編程間隔刷新,或用戶啟動刷新

DDR3的SDRAM控制器可作為IPexpress用戶可配置的IP核,能夠進行IP的配置,生成網表和模擬文件用于設計。請注意,除非購買了這個IP 的許可證,否則生成的位流可能會被阻止,或比特流可能有時間邏輯。

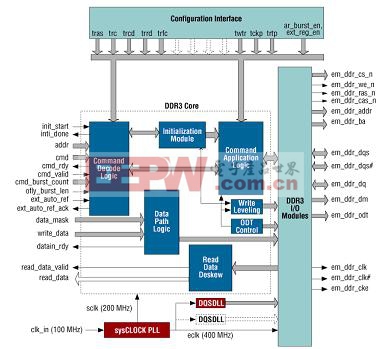

圖2:DDR3存儲器控制器IP核框圖

評論