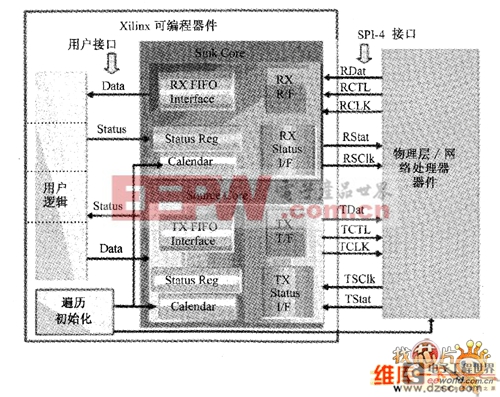

SPI-4接口的數(shù)據(jù)處理

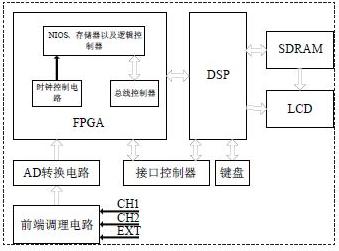

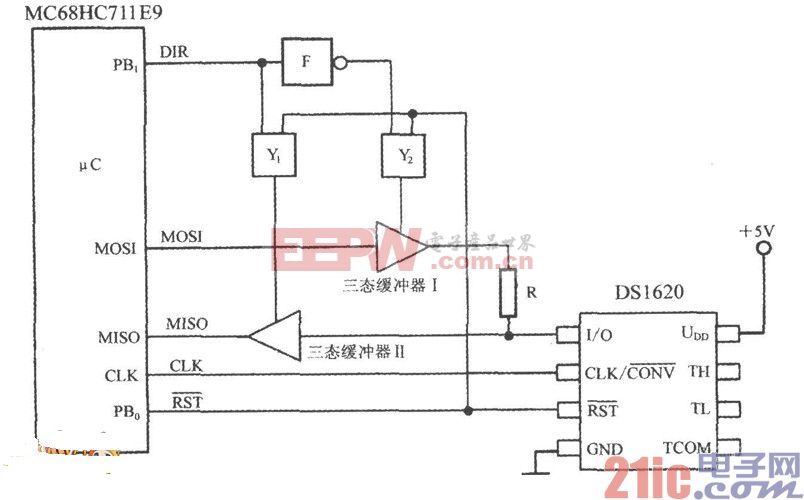

圖1 Xilinx SPL-4解決方案框圖

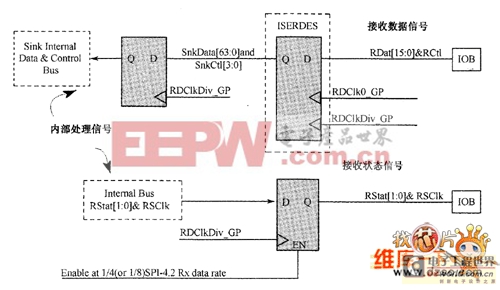

(1)Sink Core I/0接口設(shè)計(jì)

對(duì)于數(shù)據(jù)通道,Sink Core的接收數(shù)據(jù)在FPGA I/O內(nèi)部通過(guò)ISERDES串并轉(zhuǎn)換后,把數(shù)據(jù)速率降低供內(nèi)部處理。這樣做的目的是降低了FPGA內(nèi)部系統(tǒng)頻率,使時(shí)序更加容易滿足。而對(duì)于狀態(tài)信`患通道,把內(nèi)部處理的數(shù)據(jù)直接經(jīng)過(guò)LO里的寄存器鎖存輸出,如圖2所示。

圖2 Sink Core I/O接口

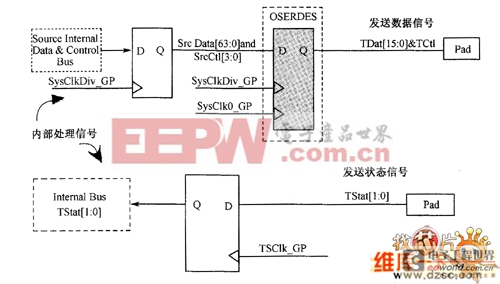

(2)Source Core I/O接口設(shè)計(jì)

Source Core的處理是內(nèi)部已經(jīng)處理好的數(shù)據(jù)經(jīng)過(guò)FPGA I/O內(nèi)部的OSERDES進(jìn)行并串轉(zhuǎn)換輸出。而對(duì)于狀態(tài)信息通道,因?yàn)樗俾时容^低,最高不超過(guò)數(shù)據(jù)通道速率的1/4。所以處理起來(lái)比較簡(jiǎn)單,直接使用FPGA I/O內(nèi)部的寄存器鎖存輸出到內(nèi)部處理即可,如圖3所示。

圖3 Source Core I/O接口

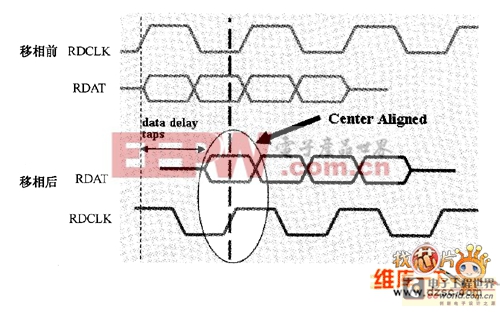

(3)DPA功能

對(duì)于數(shù)據(jù)對(duì)齊來(lái)說(shuō),由于在SPI-4中允許數(shù)據(jù)的偏移為±1個(gè)BIT,所以除了要做位對(duì)齊外,還需要做通道對(duì)齊。位對(duì)齊就是利用Xilinx Vitex-5器件內(nèi)部的IODELAY模塊用移相狀態(tài)機(jī)在其上面進(jìn)行移相。多達(dá)64級(jí),每級(jí)大約75ps,直到采樣時(shí)鐘對(duì)齊到數(shù)據(jù)窗口的中間位置。位對(duì)齊的效果如圖4所示。

圖4 位對(duì)齊效果

通道對(duì)齊利用協(xié)議指定的Training Pattern作為對(duì)齊信息和ISERDES模塊中的BITSLIP功能來(lái)進(jìn)行,效果如圖5所示。

圖5 通道對(duì)齊前后效果

只有完成這兩個(gè)對(duì)齊過(guò)程,接收端的輸入數(shù)據(jù)才真正被處理完畢,這時(shí)數(shù)據(jù)就可以直接供給內(nèi)部做協(xié)議處理。

(4)用戶FIFO

該FIFO用于與用戶邏輯連接的,其原理是把內(nèi)部協(xié)議處理后的數(shù)據(jù)寫入FIFO,然后讀出FIFO的數(shù)據(jù)作為后級(jí)的用戶邏輯使用。有機(jī)地隔離了用戶邏輯和用戶FIFO,使用戶邏輯的設(shè)計(jì)更加清晰和容易。

(5)參數(shù)配置

該模塊主要做參數(shù)配置作用,用來(lái)配置支持的端口數(shù)、最大發(fā)送包長(zhǎng)、遍歷長(zhǎng)度及連續(xù)的DIP4和DIP2有效數(shù)目等。

評(píng)論