CPU接口芯片GT-48330在網管交換機中的應用

2.2 工作原理

GT-48330作為CPU和G.Link接口的交換芯片間的橋梁,主要的工作就是將數據從交換芯片轉給CPU,這對GT-48330來講是一個接收過程;并將CPU發過來的數據轉給交換芯片,這對GT-48330來講是一個發送過程。

2.2.1 GT-48330的接收

GT-48330接收的數據分為4種:由交換芯片送過來的數據包、由交換芯片送過來的新地址消息(一個數據包只要通過交換芯片,包中的源地址信息就會被交換芯片記錄并傳送)、由交換芯片送過來的中斷消息和CPU要從交換芯片中讀取的消息。

(1)接收數據包過程 在GT-48330中存在2 kB的緩沖區(Buffer)用于接收來自交換芯片的包。由交換芯片產生的包發送結束消息(EOP)存在0x9E4 0x9EF中,當GT-48330接收到包,并監測到EOP后,他將發送相應的中斷給CPU,CPU從Interrput-cause寄存器中可以獲得中斷的原因,這樣CPU就可以從Buffer中讀取包。

當Buffer滿時,如果GT-48330還沒有完成對先 前包的處理,又有新的包到來,此時將會產生G.Link口的擁塞。GT-48330可以設置Disable PacketBlocking(DPB)bit來防止擁塞,當設為0時,GT- 48330將通過發流控消息來防止G.Link口的擁塞;當設為1時,GT-48330將通過拒絕這些包來防止擁塞,此時所有的包將被忽略。

(2)接收新地址消息的過程GT-48330中存在一個專用的新地址隊列(NA_Q),共可以存儲16個條目,對應的存儲地址為0x800~0x80F。當有新的地址到來時,GT-48330將發送一個中斷給CPU,這樣CPU就可以到0x800~0x80F中提取新的地址消息,同時將Interrput-cause0寄存器清零;如果GT-48330還有新的地址,將會把新的地址消息放入到0x800~0x80F中,并再次發出中斷。

(3)對于新地址隊列溢出的情況,GT-48330可以通 過忽略或發流控消息來處理。這可以通過設置GT48330的Enable_register<DNAB>bit來實現,而CPU可以通過監測NAQOF中斷來獲得。如果<DNAB>bit設置為1時,當NA_Q滿時,GT-48330將忽略到來的新地址消息;如果為0時,當NA_Q滿時則發流控信息,通知交換芯片,暫緩發送。

(4)CPU要從交換芯片中讀取消息的過程CPU發送消息給交換芯片,表示要獲取數據(例如一些端口狀態信息)。此時,交換芯片會發送Block_write消息給CPU,在GT-48330中有一個專用的32B的Buffer用于存儲此消息,對應的存儲地址為:0x980~0x99F。當有block_write到來時,GT-48330將發送中斷消息給CPU,CPU通過相關的中斷位獲取中斷,然后來讀取block_write消息。

2.2.2 GT-48330的發送

對于GT-48330來說他具有2種發送方式:自動DMA方式和CPU傳輸方式。對于自動DMA的方式,不需要CPU進行干涉,GT-48330可以自動完成發送。對于CPU傳輸方式,則需要CPU對發送的過程進行干涉。

(1)自動DMA方式 CPU首先寫傳輸數據(TD)寄存器,同時設置<TD>位,GT-48330根據TD來向交換芯片發送Buffer請求消息,在TD消息中包含了目的交換芯片號、端口號、CPU號及包的數量等消息。CPU寫數據到GT-48330的32 b的包存儲空間8LWW Buffer中,如果GT-48330接收到交換芯片可以開始傳送包的消息(SOP),他將把包發送給相應的交換芯片;如果收到交換芯片的拒絕消息(Buffer_rejecet),他將發送相應的中斷給CPU,告訴發數據被拒絕。

(2)CPU傳輸方式 CPU先直接通過GNT-A/B Buffer來發送Buffer請求消息,CPU等待接收到SOP消息,此消息將被GT-48330存儲在OGRBuffer中,然后再傳給CPU。一旦CPU收到SOP消息,就通過GT-48330的GNT-A/B通道來發送數據包,同時CPU還通過GNT-A/B來發送數據包傳送結束(EOP)消息給交換芯片。

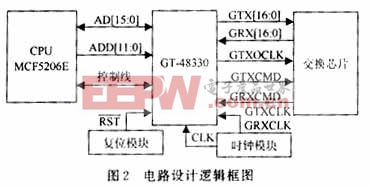

3 電路設計

GT-48330的G.Link口的電路設計說明:數據發送和接收線GTXD[15∶0]/GRXD[15∶0]與交換芯片的G.Link口的接收和發送線相連;GTXCMD/GRXCMD發送和接收與交換芯片的接收和發送命令線相連;GTXOCLK發送數據的參考時鐘,通過22Ω的匹配電阻接到交換芯片的G.Link口的接收時鐘;GRXCLK接收數據的參考時鐘,由時鐘模塊來提供;GTXCLK接收數據的參考時鐘,由時鐘模塊來提供;GTXCLK作為GT-48330的G.Link口的系統時鐘,同樣由時鐘模塊來提供。GTXCLK和GRXCLK的時鐘頻率為83.33 MHz。電路邏輯圖如圖2所示。

評論