PXI模塊觸發總線接口的CPLD實現

pxi觸發接口實現原理圖

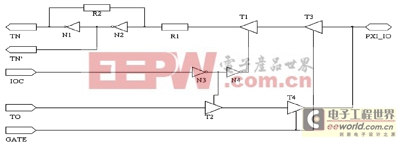

這里只給出一路觸發總線實現的原理圖,由于8路觸發總線之間是獨立工作的,因此,每一路都可以用同樣的原理來實現,只是實際應用中,8路信號可以共用一些控制線而已。一路觸發總線接口的原理如圖1所示。

圖1 觸發總線接口的原理

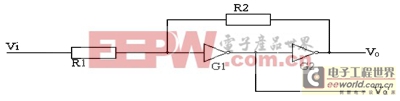

圖1所示,由n1、n2、r1、r2組成了門電路施密特觸發器,其原理圖如圖2所示。

圖2 門電路施密特觸發器的原理

圖2所示,vi為觸發器輸入端,vo為輸出端,vo為反相輸出端口,g1、g2為兩個反相器,其閾值電壓vth=0.5vdd,且電阻r1r2,則電路狀態發生轉換時其正向閾值電壓為vt+=(1+r1/r2)vth,負向閾值電壓為vt-=(1-r1/r2)vth,正向閾值電壓與負向閾值電壓的差就稱為回差電壓,即δvt=vt+-vt-=2r1/r2 vth。

圖1中,由t1、t2、n3和n4構成輸入/輸出控制部分,當ioc=1時,t1導通,t2截止,接口工作在輸入狀態,由別的模塊送來的觸發信號送入施密特觸發器進行觸發;當ioc=0時,t1截止,t2導通,接口工作在輸出狀態,觸發信號通過本接口輸出送到別的模塊進行觸發同步。

圖1中,由t3和t4組成了一個三態輸入/輸出門,當系統上電復位時,gate輸入低電平,兩個三態門均處于高阻態,直到復位結束,由軟件控制gate信號線變為高電平,三態門導通,接口處于正常的輸入/輸出狀態。

該觸發總線接口可以通過對cpld器件進行編程來實現,直接使用原理圖方式輸入。為了滿足如上所述定則2中關于i/o緩沖器直流特性的要求,這里選用5v供電電源的cpld芯片。另外,由于電阻元件在cpld中不容易實現,可以采用外接電阻的方法,這也為選擇電阻參數提供了更多的自由。

評論