基于FPGA的PCI接口設計

3.2 Memory寫操作

pci_t32的單周期memory 寫操作時序如圖3所示。

時序分析及用戶邏輯設計要點:pci主設備在第2個clk給出要寫的目標地址ad 31 0 和Memory寫命令cben 3 0 =7,pci_t32在第3個clk向用戶設備給出寫目標地址l_adro 31 0 和Memory寫命令l_cmdo 3 0 =7。用戶設備要對l_cmdo 3 0 譯碼來判斷是何種操作,對l_adro 31 0 譯碼來選擇目標地址。在lt_framen輸出為低的下個時鐘周期,若用戶設備邏輯準備好接收pci_32t寫的數據,可以置低lt_rdyn。若用戶邏輯沒有準備好,可以延遲置低lt_rdyn來產生延時等待周期。當lt_dxfrn輸出為低電平時(第7個clk),pci_t32已經將輸出的有效數據放在l_dato 31 0 上,pci用戶設備必須在第8個clk的上升沿將l_dato 31 0 輸出的數據D0鎖存至目標地址l_adro 31 0 ,用戶設備邏輯可以用第8個clk的上升沿來作為鎖存器的鎖存時鐘,用lt_dxfrn作為鎖存器的鎖存使能信號(/Latch Enable)或存儲單元的寫使能信號(/Write Enable)。

4 應用設計實例及注意事項

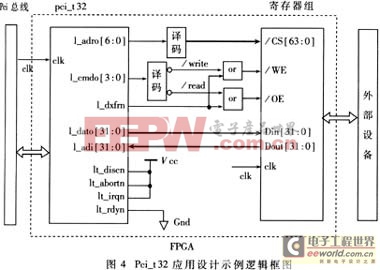

筆者已經成功地將pci_t32用于一個compact PCI的TARGET控制模塊中。在這個模塊中,主設備Master通過pci_t32來讀寫64個32bit控制寄存器,再由這些寄存器組去控制外部設備。在本系統的FPGA里,還有仲裁器等其它邏輯,PCI時鐘是33MHz,芯片選用的是EPF10K100EQC240-2。系統邏輯設計的框架如圖4所示。

在寄存器組里還有一些簡單的選通、三態控制等邏輯,此略。L_adro 6 0 譯碼選擇寄存器組里的目標寄存器。當/WE有效時,l_dato 31 0 上是pci_t32輸出的有效數據;當/OE有效時,寄存器組必須將要輸出的數據放到l_adi 31 0 總線上。

在使用pci_t32時,還有一些值得注意的地方,如下所述:

1 用戶邏輯的時鐘(本系統的寄存器組的時鐘clk)與進入pci_t32的時鐘必須是同一個時鐘,并且在定義管腳時應選用全局時鐘線(global clock)。這樣,可以保證時鐘的同步,提高系統的性能。

2 從庫中調出pci_t32.gdf的symbol,在其右上角,可以看到一些默認設置,雙擊這些參數,可以改變設置。包括:Device_ID、REVISION_ID、CLASS_CODE、VENDOR_ID、基地址等PCI標準配置寄存器。

3 選擇芯片主要考慮兩個因素:

容量和速度。芯片容量包括片內的邏輯單元和可用I/O管腳數。芯片速度主要由PCI系統工作的時鐘頻率以及用戶邏輯的大小和優化程度兩方面決定。

Pci_t32的資源占用較小,在用EPF10K100EFC484-1芯片編譯時,占用621個LC(Logic Cell)。而PCI宏核pci_a,在用EPF10K100EFC484-1芯片編譯時,占用923個LC。EPF10K100共有約5000個LC。

Altera的FPGA有多種容量和速度級,一般來說,-1速度級的芯片可以滿足66MHz時鐘的PCI時序要求,-2速度級的芯片只能滿足33MHz時鐘的PCI時序要求。

速度和容量是否能滿足用戶的要求,必須要進行仿真才能最終確定。

現在FPGA的價格日漸下降,大容量的FPGA使用越來越普遍。各家芯片供應商都提供了各種 PCI宏核邏輯。設計者可以將PCI用戶邏輯與PCI接口宏核邏輯集成在一片FPGA里,在頂層通過仿真來驗證PCI接口以及用戶邏輯設計的正確與否。這樣,可以大幅度提高調試速度,縮短開發周期,提高電路板的集成度和系統性能。可以肯定地預言,使用PCI接口宏核邏輯來進行PCI接口設計是今后設計PCI接口的主要方法。PCI接口宏核邏輯將會受到越來越多的設計工程師的青睞。

參考文獻

1 ALTERA Device Data book 1999.ALTERA,1999

2 PCI MegaCore Function User Guider,Version 1.0.ALTERA,1999年12月

3 金 革.可編程邏輯陣列FPGA和EPLD.合肥:中國科技大學出版社,1996

評論