解析基于FPGA的智能控制器設計及測試方法

圖2控制器開環時序仿真圖

圖2為基于Altera公司FPGA器件EP20K200EQC240-1的模糊自整定PID控制器閉環輸出時序仿真結果。

其中:clk:系統時鐘;clkc:控制器采樣時鐘;reset:系統復位信號;e:偏差;ec:偏差的變化率;u:控制器輸出。

時序仿真結果參數:Total logic elements:1092 / 8,320 ( 25 % );Total memory bits:4096 / 106,496 ( 3% );Clk setup:38.86 MHz;Clkc setup:221.39MHz;Tsu:8.864ns;Tco:7.809 ns。

圖2中控制器的激勵信號偏差e和偏差變化率ec是通過波形編輯器手工編輯獲得,輸入比較繁瑣,它們值的獲取是借助于MATLAB的仿真曲線,因此并不能完全模擬智能控制器的實時激勵信號。 為了能更好的模擬控制器的輸入行為,使測試結果更加可靠,本文在上述測試基礎上,提出一種新的基于FPGA設計工具QuartusII、DSP Builder以及Modelsim的智能控制器閉環時序測試方法。

5 基于FPGA的智能控制器閉環時序測試

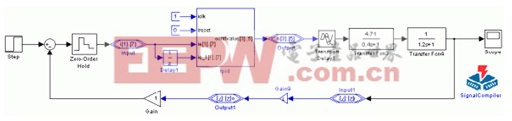

在自動控制系統設計中,控制器的設計與測試通常采用閉環控制系統,通過觀察對象的輸出來判斷控制器性能是否符合設計的要求。Altera公司推出的數字信號處理工具DSP Builder,結合MathWorks的Matlab和Simulink,為在QuartusII中所做的設計提供了一種新的測試方法。本次研究采用的測試流程如下:首先,在Matlab的Simulink中用DSP Builder搭建測試模塊,運行無誤后,用Signal Compiler將(.mdl)文件轉換成Modelsim可以識別的TCL腳本文件和VHDL文件,其次,對生成的VHDL文件及TCL腳本進行設置CONTROL ENGINEERING China版權所有,最后,在Modelsim中運行測試文件,查看測試結果。DSP Builder下模糊自整定PID控制器的模塊圖如圖3所示。圖中fpid模塊為用戶自定義模塊,是通過DSP Builder的SubSystemBuilder模塊導入的,使用該模塊可以方便的將QuartusII中VHDL設計文件的輸入輸出引腳信號引入Simulink系統中。

圖3 DSP Builder下模糊自整定PID控制器的模塊測試圖

運行Signal Compiler,生成在Modelsim中使用的TCL腳本文件控制工程網版權所有,因為在Simulink中添加的用戶自定義模塊是以黑盒的形式出現,因此,在該測試環境中要將模糊自整定PID控制器的各個子模塊文件添加到TCL腳本文件中,例如要將子模塊文件pid.vhd添加到TCL腳本文件中,使用vcom -93 -explicit -work work "$workdir/pid.vhd"即可。

使用DSP Builder時需要注意以下兩點:

(1)如果沒有使用來自Rate Change庫中的鎖相環模塊PLL,在Simulink設計轉換成硬件系統的過程中,DSP Builder將使用同步設計規則,即在設計系統中的所有DSP Builder時序模塊(如圖3中的Delay1模塊)都以單一時鐘的上升沿同步工作,這個時鐘頻率即為整個系統的采樣頻率。對于這些模塊,其時鐘引腳都不會直接顯示在Simulink設計圖上,但當使用Signal Compiler將設計轉化為VHDL文件時,系統會自動地把時序模塊的時鐘引腳都連在一起,并與系統的單一時鐘相接。

(2)將一個已經定制完成的VHDL設計實體加入到DSP Builder設計系統中時CONTROL ENGINEERING China版權所有,即使在原設計中已經使用了同步復位和時鐘信號,也必須在該實體中定義同步清零和時鐘輸入信號。而且,這兩個輸入信號必須與目標器件的全局時鐘引腳和全局同步清零引腳相接。如果實體不需要時鐘或全局同步清零腳,也應當定義這些輸入信號,只是不要連接。

以被控對象G(s)=4.71×e-0.15s/(0.4s+1)(1.2s+1) 為例,考慮到A/D、D/A的影響,加入零階保持器(1-e-TS)/S,Modelsim中閉環控制系統的輸出曲線如圖4所示,系統的給定值為127(相對增益為0.992),輸出值從0上升到峰值148(相對增益為1.156)后迅速回落,最后穩定在127,測試結果與MATLAB的仿真結果基本相同。

圖4 系統閉環輸出曲線

6 結 論

(1) 基于FPGA構建智能控制器具有設計靈活、能在線調整、可靠性高,開發周期短等優點。特別適于中小型系統。

(2) 利用QuartusII進行智能控制器的VHDL設計,通過DSP Builder和Modelsim對在QuartusII中所做的設計進行閉環測試,解決了測試樣本的輸入源以及控制器的輸入樣本提取問題,能有效模擬控制器的輸入行為,提高了設計及測試的靈活性,同時,測試結果可靠且更有說服力。

(3) 使用DSP Builder和Modelsim使我們擺脫了以往的測試習慣,控制器的激勵輸入信號可以方便的調用Simulink的模塊,對象也可以根據需要靈活改變,不需要再用VHDL語言編寫,而且Modelsim支持信號的模擬波形顯示,使我們能夠看到最直觀的圖形。

(4) 測試在系統設計中占有舉足輕重的作用,它貫穿整個設計的始終,采用閉環時序測試方法,結合DSP Builder和Modelsim完成智能控制器各個階段的測試經實驗驗證是一較好的測試方法,適合于像控制器這類需閉環檢驗其控制品質的設計。

評論