FlexRay的通信控制器媒體接入控制設計

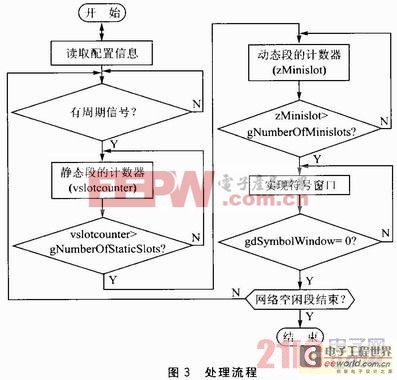

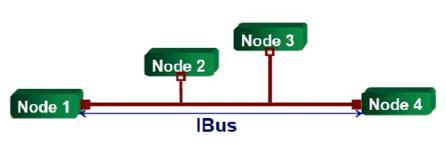

具體處理流程如圖3所示。

2 設計驗證

確保設計正確性的關鍵是設計驗證,主要通過邏輯功能仿真。邏輯功能仿真是在不考慮信號延遲的情況下對設計的邏輯功能進行驗證。驗證過程是:首先編寫好設計的HDL代碼;然后編寫對應的TestBcnch,對設計進行關鍵性的驗證;最后利用仿真軟件ModelSim進行模擬,查看波形或者輸出,若發現錯誤則查找錯誤原因、修改代碼或者測試文件,直到符合設計要求。

設計驗證的首要工作是根據FlexRay協議設定具體的參數。具體參數的設定如下:gMacroPcrCycle=48,gdStaticSlot=4,pMicroPerCyc le=672,gNumberOfMinislots=15,gdSymbolWindow=3,gdActionPointOffsct=1,gdMinislotActionPointOffset=1。

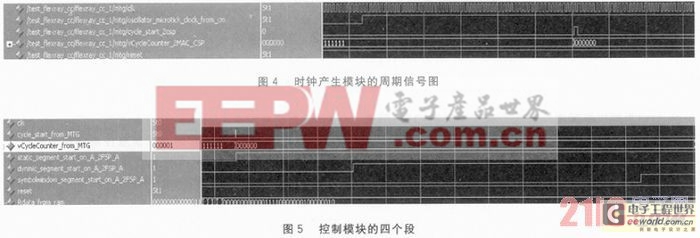

圖4是時鐘產生模塊的周期信號圖。從圖中可以看到,時鐘產生模塊需要等待晶振的最小時鐘節拍信號,然后進行判斷產生周期信號。當周期信號開始時,周期編號從默認的63變為0,然后一直編號下去直到63。

圖5是對圖4產生的周期信號開始周期的四個段的劃分。從圖中可以看到,0周期分為靜態段、動態段、符號窗口、網絡空閑段。

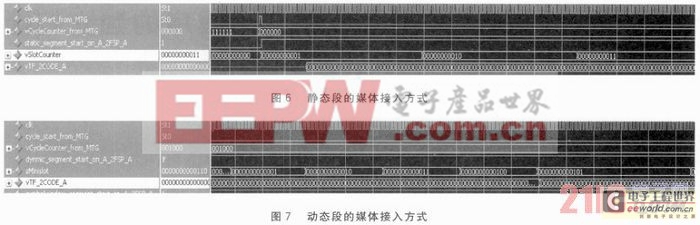

圖6是靜態段的媒體接入方式。從圖中可以看到,槽計數器(vslotcounter)從1開始編號直到用戶配置的值。在第一個靜態槽實現了媒體接入。

圖7是動態段的媒體接入方式。從圖中可以看到,周期8的動態段有動態槽計數器zMinislot,從0開始編號直到用戶配置的值。在第5個動態槽實現了媒體接入。

結語

本文介紹了基于FlexRay協議的媒體接入控制的設計過程,并進行了設計驗證。從仿真結果分析,它符合協議的要求,能夠生成通信控制器的時鐘周期,將時鐘周期進一步劃分為4個段,并且給出靜態段和動態段的具體媒體接入方式。

評論