基于EMIF接口的DSP控制系統(tǒng)設(shè)計

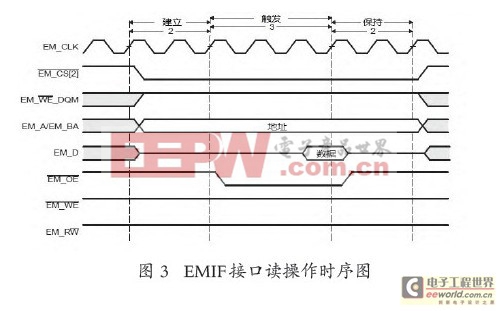

一個EMIF讀操作分為建立時間、觸發(fā)時間和保持時間三部分。在建立時間開始時,EM_CS[2]片選信號拉低,同時地址線EM_A 與EM_BA 給出所讀取數(shù)據(jù)的地址。觸發(fā)時間開始時,EM_OE信號拉低,同時FPGA在EM_D信號線上傳輸數(shù)據(jù),DSP將在觸發(fā)時間的最后一個時鐘處對數(shù)據(jù)采樣。保持時間中EM_OE 信號將拉高,并在保持時間結(jié)束后,EM_CS[2]信號拉高。在整個周期中EM_WE_DQM、EM_WE、EM_RW信號始終為高電平。

2.2.2 異步寫操作

DSP發(fā)出對FPGA的寫申請時,就會進行異步寫操作。當(dāng)寫操作不能在外部器件的一個訪問周期內(nèi)完成時,EMIF就會進行多個周期的操作,直到完成整個申請。

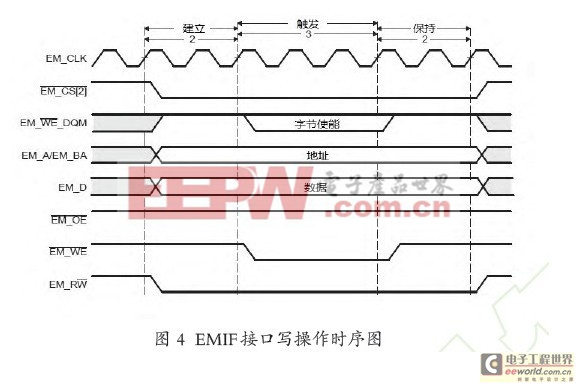

類似于讀操作,EMIF 寫操作分為建立時間、觸發(fā)時間和保持時間三部分。在建立時間開始時,EM_CS[2]片選信號拉低,EM_RW信號拉低,同時地址線EM_A與EM_BA給出所讀取數(shù)據(jù)的地址,數(shù)據(jù)線EM_D給出需要寫入FPGA的數(shù)據(jù)。觸發(fā)時間開始時,EM_WE信號拉低,EM_WE_DMQ信號給出字節(jié)使能信號。保持時間開始時EM_WE_DMQ信號與EM_WE信號拉高,并在保持時間結(jié)束后,EM_CS[2]信號與EM_RW信號拉高。在整個寫操作周期中EM_OE信號始終為高電平。

DSP 通過配置EMIF 接口的寄存器來實現(xiàn)上述時序,F(xiàn)PGA可采用IP 核來實現(xiàn)EMIF協(xié)議,不同的FPGA芯片要采用不同的地址。

3 系統(tǒng)BOOT 方法

TMS320C6722 型DSP的內(nèi)部沒有可寫的ROM,DSP的程序必須存放在外部器件中,DSP 芯片上電后必須首先從外部芯片下載程序。本款DSP可以通過SPI 總線啟動、通過I2C總線啟動和通過EMIF接口啟動。這幾種Boot 方式和對應(yīng)的引腳配置如表1 所示,在本系統(tǒng)中,EMIF接口除了實現(xiàn)通常的數(shù)據(jù)交換,還兼任帶動DSP啟動的功能。

系統(tǒng)上電后,DSP 的RESET 引腳要通過下拉電阻拉低,使DSP 處于復(fù)位態(tài)。FPGA 芯片EP2C8F256I8 上電后從FPGA 配置芯片EPCS4 中下載程序啟動。FPGA啟動成功后將DSP芯片的SPI0SOMI 引腳與SPI0CLK 引腳拉低,將SPI0SIMO 引腳拉高,然后再將RESET引腳拉高。這樣配置是為了使DSP退出復(fù)位態(tài)時能根據(jù)上述3 個引腳的電平獲知DSP 芯片將通過EMIF接口啟動。此后,DSP芯片將從EMIF 接口讀取1KB數(shù)據(jù),并將這1KB數(shù)據(jù)存放于DSP的RAM中,再執(zhí)行這1KB的程序。

上述過程稱為DSP的第一次啟動過程。這1KB的程序是由匯編語言編寫并通過CCStudio 軟件編譯成機器語言,存放于FPGA中(通過mif 文件編譯進FPGA的程序)。該1KB程序的功能是再次調(diào)用EMIF 接口,操作FPGA,使得FPGA 通過IP 核從FLASH芯片中將其余的程序(本系統(tǒng)的程序約為32K)拷入DSP的RAM 中并執(zhí)行這些新拷入的程序。這是DSP 的第二次啟動。第一次啟動是硬件啟動,是TMS320C6722 型DSP已經(jīng)設(shè)定好的啟動方式,第二次啟動是軟件啟動,所執(zhí)行的啟動程序由用戶編寫。

綜上,本文介紹了DSP芯片通過EMIF接口連接FPGA的硬件電路與時序,根據(jù)本文介紹的方法,DSP芯片通過FPGA能控制大量外部芯片工作,僅使用DSP的EMIF接口就能實現(xiàn)DSP啟動和控制復(fù)雜系統(tǒng)工作的功能,大大擴展了DSP芯片的靈活性,使其強大的運算功能得以更好的發(fā)揮。

陀螺儀相關(guān)文章:陀螺儀原理

評論