標(biāo)準(zhǔn)接口的基本技術(shù)知識(shí)

DDR2/移動(dòng)DDR

DDR2 是雙陪數(shù)據(jù)速率 (DDR) SDRAM規(guī)范的后繼標(biāo)準(zhǔn),這兩個(gè)標(biāo)準(zhǔn)互不兼容。DDR2 在總線時(shí)鐘信號(hào)的上升沿與下降沿傳輸數(shù)據(jù),并能夠以更高的總線速度運(yùn)行,從而可實(shí)現(xiàn)每個(gè)內(nèi)部時(shí)鐘周期四次的數(shù)據(jù)傳輸。

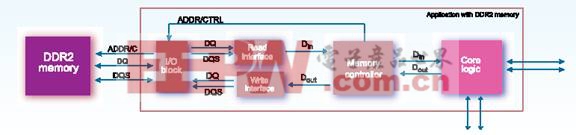

簡(jiǎn)化型 DDR2 控制器包括以下設(shè)計(jì)塊:

· 存儲(chǔ)器控制;

· 讀取接口;

· 寫入接口;

· 以及 IO 塊。

這些塊以及它們與 DDR2 存儲(chǔ)器芯片及核心邏輯的關(guān)系見(jiàn)圖 2 所示。

圖 2:簡(jiǎn)化型 DDR2 控制器的實(shí)施

存儲(chǔ)器控制塊發(fā)出存儲(chǔ)器對(duì)專用核心邏輯的訪問(wèn),反過(guò)來(lái)也是如此。讀取物理塊負(fù)責(zé)處理在各個(gè)讀取周期中采集數(shù)據(jù)的外部信號(hào)時(shí)序,而寫入物理塊則使用適當(dāng)?shù)耐獠啃盘?hào)時(shí)序管理時(shí)鐘與數(shù)據(jù)的發(fā)出。

字節(jié)寬度雙向數(shù)據(jù)選通 (DQS) 隨數(shù)據(jù) (DQ) 通過(guò)外部方式傳輸,用于采集目的。DQS 在讀取存儲(chǔ)器時(shí)由控制器通過(guò)邊緣對(duì)齊的方式傳輸,而在寫入存儲(chǔ)器時(shí)則采用中心對(duì)齊的方式。片上延遲鎖相環(huán) (DLL) 用于鎖住 DQS 及相應(yīng)的 DQ.這可在電壓及溫度發(fā)生變化時(shí)確保它們能夠彼此跟蹤。

路由器相關(guān)文章:路由器工作原理

路由器相關(guān)文章:路由器工作原理

交換機(jī)相關(guān)文章:交換機(jī)工作原理

存儲(chǔ)器相關(guān)文章:存儲(chǔ)器原理

評(píng)論