基于FPGA的視頻圖像分割技術(shù)設(shè)計(jì)與應(yīng)用

數(shù)字硬盤錄像機(jī)是一種性價(jià)比很高的視頻監(jiān)控解決方案,具有對(duì)圖像/語音進(jìn)行長(zhǎng)時(shí)間錄像、錄音、遠(yuǎn)程監(jiān)控和控制的功能,集合錄像機(jī)、畫面分割器、云臺(tái)鏡頭控制、報(bào)警控制、網(wǎng)絡(luò)傳輸?shù)裙δ苡谝簧恚悄壳笆忻嫔弦曨l監(jiān)控系統(tǒng)的首選產(chǎn)品。在DVR系統(tǒng)中,需要在一個(gè)現(xiàn)實(shí)設(shè)備上同時(shí)顯示多個(gè)監(jiān)控畫面,這樣可大大節(jié)省資源并便于工作人員監(jiān)視,本文研究的內(nèi)容就是這種圖像分割技術(shù)在FPGA上的實(shí)現(xiàn)。

FPGA是20世紀(jì)80年代由美國Xilinx公司首先推出的,它具有性能高、規(guī)模大、可重復(fù)編程、開發(fā)投資小等優(yōu)點(diǎn),在現(xiàn)代電子產(chǎn)品設(shè)計(jì)中應(yīng)用廣泛。FPGA具有極高并行度的信號(hào)處理引擎,提供高性能的信號(hào)處理能力。在本設(shè)計(jì)中,就是要利用FPGA的高速性能對(duì)多路視頻信號(hào)進(jìn)行處理,從而簡(jiǎn)化硬件結(jié)構(gòu),提升DSP性能,使單片DSP實(shí)現(xiàn)16路CIF圖像實(shí)時(shí)編解碼成為可能。

1 圖像分割與合成

1.1視頻標(biāo)準(zhǔn)

FPGA處理的視頻數(shù)據(jù)由專用解碼芯片Tw2815輸出,符合ITU.RBT.656標(biāo)準(zhǔn)。ITU.RBT.656標(biāo)準(zhǔn)是在國際電信聯(lián)盟無線電通信部門656.4號(hào)建議書中提出,全稱是工作在ITU.RBT.601建議(部分A)的4:2:2級(jí)別上的525行和625行電視系統(tǒng)中數(shù)字分量視頻信號(hào)的接口。實(shí)施這樣的標(biāo)準(zhǔn)是為了在525行和625行兩者間提供一種世界范圍兼容的數(shù)字化方法。數(shù)據(jù)信號(hào)編碼成8比特二進(jìn)制信息形式,格式如圖1所示。

由圖1可知ITU.RBT.656并行接口除了傳輸4:2:2的YCbCr視頻數(shù)據(jù)流外,還有行、列同步控制信號(hào)。一幀數(shù)據(jù)由525行(NTSC制式)或625行(PAL制式)、每行1728個(gè)字節(jié)的數(shù)據(jù)塊組成。每行數(shù)據(jù)中,有4個(gè)字節(jié)的EAV和SAV信號(hào),前3個(gè)字節(jié)是前導(dǎo)數(shù)據(jù),最后一個(gè)字節(jié)中包含本行數(shù)據(jù)信息。EAV/SAv包含了關(guān)于同步的所有信息。

1.2 割與合成原理

視頻圖像合成基于像素域,即將多路壓縮的源視頻編碼數(shù)據(jù)進(jìn)行解碼,將解碼后的YUv(或RGB)數(shù)據(jù)按照一定線性規(guī)則進(jìn)行排列,合并成一路ⅥⅣ(或RGB)數(shù)據(jù),再將合并后的視頻數(shù)據(jù)進(jìn)行編碼12J。ITU.RBT.656標(biāo)準(zhǔn)YCbC,(4:2:2)格式中4:2:2的含義為Y信號(hào)與Cb、C,信號(hào)的數(shù)量比為4:2:2,即在有效視頻數(shù)據(jù)區(qū)域,每4個(gè)字節(jié)為一個(gè)宏像素點(diǎn),其中包含2個(gè)Y信號(hào),1個(gè)Cb信號(hào)和1個(gè)Cr信號(hào)。

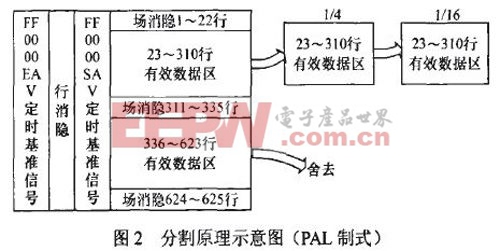

要實(shí)現(xiàn)4畫面及16畫面顯示功能,就是要以宏像素為單位對(duì)原畫面像素按照1/4(或1/16)的比例進(jìn)行抽取,如圖2所示(以PAL制式一幀數(shù)據(jù)為例)。

通過上面的方法可以得到各視頻通道1/4(或1/16)畫面數(shù)據(jù)接下來的任務(wù)是將畫面合成并傳輸給DSP做編碼處理。通過實(shí)驗(yàn)得到:對(duì)于TMS320DM6467芯片的VPIF(視頻設(shè)備接口)來說,只要輸入視頻數(shù)據(jù)有效數(shù)據(jù)行內(nèi)從EAV到SAV之間的字節(jié)數(shù)為一定值(可由DSP內(nèi)部寄存器設(shè)置),且行數(shù)滿足對(duì)應(yīng)制式要求,DSP就能將其識(shí)別為一幀有效數(shù)據(jù)。這樣就能得到圖3所示的第一種畫面合成方法。這種方法雖然可行,但是可以看到,在有效數(shù)據(jù)區(qū)中每一行都由多個(gè)通道數(shù)據(jù)組成,在從內(nèi)存讀取數(shù)據(jù)時(shí)通道切換頻繁。會(huì)給編碼和調(diào)試帶來困難。

評(píng)論