基于DSP和FPGA的視頻編碼器

1 硬件設計方案

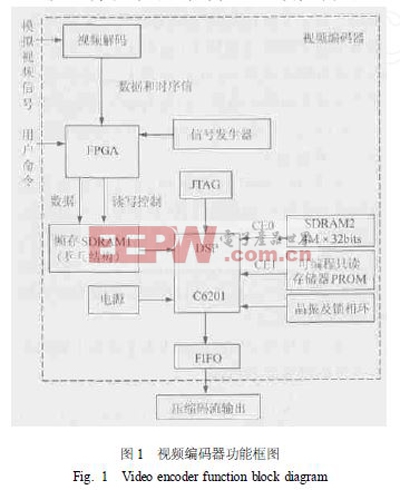

基于TI公司的圖像開發工具包(Imaging Developer Kit,即IDK)[2]架構,設計了視頻編碼器的硬件平臺。從整體上來講,視頻編碼器的硬件實現由DSP和FPGA兩個模塊組成,其邏輯框圖如圖1所示。由于視頻壓縮編碼計算量很大,為了盡可能提高視頻壓縮幀率,由DSP專門負責視頻壓縮編碼,而視頻采集、YUV轉換和編碼器I/O接口等其它功能則交由FPGA模塊來實現。

如圖1所示,用戶控制命令(例如視頻壓縮模式)由FPGA模塊首先截獲,然后FPGA模塊向DSP模塊產生外部中斷,DSP在響應中斷時讀取存儲在FPGA中的用戶控制命令字,然后DSP解析命令字,并根據用戶要求的視頻格式、幀圖像分辨率和視頻壓縮碼流速率進行視頻壓縮編碼。

模擬視頻信號經視頻解碼器轉換為裸視頻數據流,該數據流(或從數字攝像機直接獲得的數據流)經FPGA預處理后送入幀存中。DSP讀取幀存中的數據進行壓縮編碼,壓縮后的視頻數據送入FIFO中,最后FIFO中的數據通過串口送給信道編碼器。

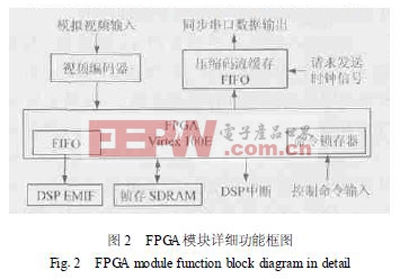

FPGA模塊的邏輯框圖見圖2。如圖2所示,視頻解碼器首先將模擬視頻信號量化為復合的YUV數據,然后經FPGA進行YUV分離(和濾波)后送到幀存(圖1中的SDRAM1)中,C6201使用DMA通道(異步方式)通過FPGA讀取幀存中的YUV數據進行壓縮編碼。幀存(SDRAM1)在刷新(refresh)或缺頁(pagemiss)時會引起DMA讀等待,為了平滑這種等待引起的DMA讀數據的抖動,設計時在FPGA的內部實現了一個高速FIFO。視頻幀存采用了乒乓結構,將8M字節SDRAM分為兩個4M字節的地址空間(每一個地址空間可以容納一幀YUV視頻數據(720×576×115字節)),一個地址空間用于存儲當前正在采集的視頻數據,另一個地址空間用于DSP的數據讀取。在壓縮CCIR601格式的視頻圖像(每秒25幀)時,由于DSP的處理速度(大約每秒10幀)慢于視頻采集的速度,所以FPGA模塊在采集完一幀數據進入等待狀態,直到DSP壓縮完上一幀視頻數據時,這2個地址空間才進行互換。

DSP模塊接收FPGA模塊送過來的YUV視頻數據,然后進行視頻壓縮編碼,最后將壓縮的碼流再轉交給FPGA模塊,由FPGA模數據發送出去。DSP模塊的存儲單元(圖1中的SDRAM2)用來存放參考幀數據和中間運算結構。MPEG-4壓縮編碼算法指令存放在PROM中,為縮短取指時間,編碼器在啟動時已將指令從PROM讀到片內存儲器中。MPEG壓縮碼流是變速碼流(VBR),而當該碼流在恒定速率(CBR)的信道上發送時,需要一個FIFO緩存來平滑編碼器輸出碼率的波動。

該設計的特點主要表現在以下2個方面:

①可擴展性好。FPGA模塊除了負責數據I/O功能外,還作為協處理器使用,可根據需要增加FPGA的門數來實現原來由DSP完成的功能,例如Huffman編碼、運動估計等;

②靈活的視頻壓縮編碼格式控制,編碼器能夠實時地根據用戶的要求進行壓縮編碼。

評論