基于PCI總線的1553B總線接口卡設計

在航電系統的研制初期,通常要先在地面以微型計算機為基礎做各種仿真實驗。這使得用于各仿真系統的接口板的研制和革新工作便同時成為航電系統發展的一個重點。接口板的主要任務是實現航電系統的數據總線與PC機的數據總線之間的通信功能,這使PC機可以模擬航電系統數據總線上所掛接的實際子系統。PCI(Peripheral Component Interconnect)總線,即外圍部件互連總線,是一種先進的高性能32/64位地址數據復用局部總線,可同時支持多組外圍設備。PCI局部總線不受制于處理器,為中央處理器及調整外圍設備提供一座橋梁,更可作為總線之間的交通指揮員,提高數據吞吐量,具有支持線性突發傳輸、極小的存取延誤、采用總線主控和同步操作、兼容性強等優點。本文設計了一種基于PCI總線的接口板,其服務對象是MIL-STD-1553B總線,并編寫其在Windows下的驅動程序。

1 1553B總線協議

MIL-STD-1553B是一個關于數據總線電器特性和協議規范的軍事標準,這個標準規定了飛機內部數字式的命令/響應時分制多路數據總線的技術要求,也規定了多路數據總線的操作方式和總線上的信息流的格式以及電氣要求。其作用是提供一個在不同系統之間的傳輸數據和信息的媒介。

1553B數據總線以異步、命令/響應方式執行數據信息的傳輸,是一種計雙工通信方式,它有3種終端類型:總線控制器(BC)、遠程終端(RT)和總線監視器(BM)。BC是總線上惟一被安排為執行建立和啟動數據傳輸任務的終端,BC控制數據總線上所有數據信息的傳輸,任何時候總線上只有一個BC。RT是用戶子系統到數據總線上的接口,它在BC的控制下提取數據或吸收數據。MT“監控”總線上的信息傳輸,以完成對總線上的數據源進行記錄和分析,但它本身不參與總線的通信。各終端之間信息傳輸方式有:BC到RT,RT到BC,RT到RT,廣播方式和系統控制方式。1553B數據總線上的信息流由消息組成,一個完整的消息包括命令字、數據字和狀態字3種類型。每個字的字長為20 b,其前3位為同步字頭,有效信息位是16位,最后一位是奇偶校驗位,采用奇校驗,消息字采用曼徹斯特Ⅱ型碼調制信號,所有消息格式都是基于前面所述的3種字類型。

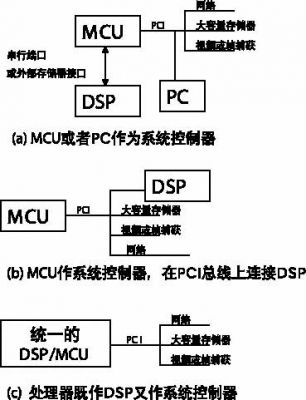

2 系統設計方案

系統設計分為2個部分:硬件電路的設計和軟件驅動程序及應用程序的設計。

2.1 系統硬件設計

系統完整的硬件電路結構如圖1所示,主要包括1553B總線接口模塊、PCI總線接口模塊和邏輯控制模塊。系統設計主要實現1553B總線和PCI總線之間的通信,因為在1553B總線上傳輸的是雙極性差分信號,所以要對發送或接收的信號進行電平轉換和相應的調制解調,1553B總線接口模塊即用來完成數據的組織和編碼或解碼。PCI總線接口模塊完成接口卡與上位機的通信。雙端口RAM作為2個模塊的數據中繼,邏輯控制模塊則將這2個模塊連接成為一個系統。上位機通過PCI總線接口模塊將欲發送的數據存入雙端口RAM中,邏輯控制模塊根據通信協議將數據送到1553B總線接口模塊,1553B總線接口模塊將此數據進行組織和編碼,發送到1553B主總線上;或1553B總線接口模塊從主總線上接收到數據,進行解碼并存放在存儲器。然后通知上位機,上位機通過PCI總線接口模塊從存儲器中取出數據以及本次1553B總線操作的狀態信息。

2.1.1 1553B總線接口模塊設計

1553B總線接口模塊主要包括1553B協議芯片、隔離變壓器和時鐘晶振。1553B協議芯片采用DDC公司的BU-61580,芯片包含2個低功耗的雙端收發器、協議邏輯、存儲器管理邏輯、處理器接口邏輯及4K×16 b內置共享靜態RAM以及直接面向主處理器的緩存接口組成,最多可擴展64K×16 b的外部RAM。協議芯片通過短截線與1553B主總線相連。而在協議芯片與短截線之間需要設置隔離變壓器,該隔離變壓器將1553B主總線與接口卡直流隔離,防止接口卡上產生的噪聲影響1553B主總線上的信號。

BU-61580功能上集成了BC/RT/BM一體化設計,可以編程設置BU-61580的配置寄存器來設定系統的工作方式,例如本系統中,通過軟件編程BU-61580配置寄存器1的位15為邏輯“1”,位14為邏輯“0”,可使BU-61580工作于RT方式。內存管理模式可選是BU-61580的RT的一大特點。為了下位機處理器可以方便的存取從給定地址接收有效的、完整的數據塊,保證為處理器提供最高程度的數據采樣一致連貫性,RT方式的內存管理采用雙緩沖模式,該模式下可以有選擇地將接收的廣播消息分解為非廣播消息。具體實現方法是為每一個接收到的消息提供2個32位的數據字塊,一個為激活的,另一個為停止的。當前命令結束后,BU-61580自動切換該子地址的數據塊的激活區域與停止區域,這樣,當向同一子地址發送命令時,如果數據有效并且雙緩沖區允許,數據會保存到另一個數據塊中,而不會使上一次的數據被覆蓋。

與下位機連接方面,BU-61580的接口配置采用16位緩沖模式,它向下位機提供了一個直接共享RAM接口。在該模式下,BU-61580的數據、地址總線與主機的總線地址隔離,并且BU-61580的尋址空間限制在其內部RAM4K字的范圍內。

2.1.2 邏輯控制模塊設計

PCI總線接口模塊與1553B總線接口模塊之間的邏輯控制電路通過可編程邏輯器件和DSP實現。可編程邏輯器件采用了Altera公司的EP1C 12B芯片,其主要實現地址譯碼、數據緩存、邏輯控制、握手連接和與BU-61580的協議轉換等功能。EP1C12B芯片內部的RAM資源作為雙端口RAM和BU-61580之間的數據通道。下位機主控單元DSP控制器采用TI公司的TMS320F2812,用于控制EP1C12B完成1553B總線接口模塊對雙端口RAM的數據吞吐。上位機對1553B協議芯片進行操作時,相應的數據信號、地址信號和控制信號通過PCI總線發送到雙口RAM中。DSP控制FPGA從雙口RAM中取出該地址信號和控制信號進行譯碼,產生對應的地址信號以及控制信號送到BU-61580。如果操作是向1553B主總線發送數據,則同時將數據信號送到BU-61580的數據線。一次讀寫操作結束時,BU-61580將輸入FPGA的READY信號拉低,通知FPGA讀寫操作結束。如果有中斷產生,則在輸入FPGA的INT引腳上產生中斷波形(下降沿或低電平)。根據BU-61580輸入FPGA的中斷信號、握手信號或數據信號等,FPGA相應產生上位機需要的中斷信號、握手信號、插入等待信號和數據信號等,送到PCI總線上。

2.1.3 PCI總線接口模塊

PCI總線接口模塊包括PCI協議芯片及其配置電路。PCI協議定義了嚴格的電氣特性和時序要求,其接口電路實現難度大,采用專用的PCI接口芯片,可以避開復雜的PCI協議的細節設計,大大縮短開發周期。本系統選用的是PLX公司生產的PCI9052接口芯片作為PCI總線控制器,實現接口卡與PCI總線的橋接。

評論