基于NiosII的圖形用戶接口的設計

1 系統總體結構設計

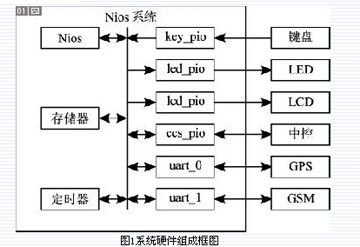

系統主要由以下4部分組成:(1)VGA控制器、SDRAM控制器、SRAM控制器等外設接口的設計。(2)Nios II軟核SOPC系統的配置。(3)Nios II處理器與外設模塊的融合。(4)GUI函數庫的建立。系統主要分為硬件和軟件兩部分,部分硬件采用DE2上的硬件電路,其中有些電路的控制器采用硬件描述語言生成;軟件則采用Nios II編譯器書寫。

2 VGA時序控制模塊設計

由于要實現VGA的實時顯示,便需要給VGA一個顯存,使得VGA顯示的信息能夠緩存和切換。出于速度的考慮,顯存模塊的讀寫速度要求較高,否則會出現卡殼現象。可采用的存儲器分別有Flash,SRAM,SDRAM,其中SRAM的速度較快,可以選用。是一種具有靜止存取功能的內存,無需刷新電路即能保存其內部存儲的數據,具有較好的存儲性能。

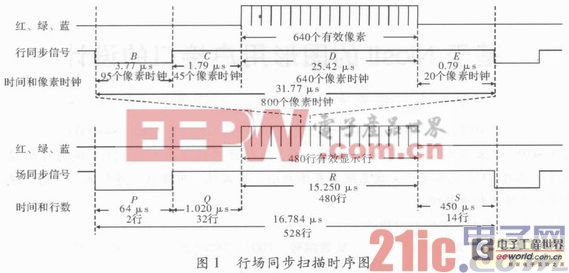

常見的VGA彩色顯示器,通常由CRT(陰極射線管)構成。彩色由紅、綠、藍三基色構組成。顯示是用逐行掃描的方式解決,一般把要顯示的數據存放于存儲器單,如果要把存儲器里的圖像顯示在VGA顯示器上,以640×480,59.94 Hz(60 Hz)為例。具體行場同步時序要求如圖1所示。

根據上述的時序參數以及目標板上的時鐘頻率,對其行頻和場頻的時序控制采用點和行計數的方法,場信號和行信號按照時序圖設計,當像素或行數達到相應的狀態后即改變場信號和行信號的值。系統所需的像素時鐘可以用鎖相環實現。

3 VGA數據緩存模塊設計

數據緩存模塊式通過Altera提供的SOPC工具中,Avalon總線上掛的一個SRAM控制器來實現數據的讀寫功能,Avalon總線與SRAM的接口對用戶是透明的。只需編寫Avalon主端口模塊,用于控制Avalon總線的主端口信號,從而實現數據的讀寫。Avalon總線同時被2個主外設共同使用,Nios II處理器將需要顯示的數據通過主端口寫入到SRAM,VGA顯示模塊通過主端口將數據從SRAM中讀出到VGA接口顯示器上顯示。當系統中存在多個主外設時,SOPC系統會自動進行總線仲裁,產生一個優先級,控制對Avalon總線的使用情況。

當某主外設要發起總線請求時,可能Avalon總線不能馬上作出響應而處于等待狀態。Nios II處理器將準備顯示的數據發送后要求立即存入到存儲器中,否則到下一個周期數據將會更新,從而導致數據丟失,此時Avalon總線需將信號設置為等待狀態。因此必須將數據暫時存儲在緩沖區中,待Avalon總線響應寫傳輸時再將其從緩沖區中讀出寫入到存儲器中。用一個先進先出的FIFO作為緩沖器能夠滿足以上條件,通過時鐘來控制FIFO的寫入和讀出。

4 結束語

試驗結果證明,運行在FPGA中的SOPC系統可以控制VGA顯示器,并將VGA成功驅動,而且能夠進行畫點、畫線、畫矩形、畫圓以及16×16漢字和8×16 ASCII字符混排的顯示,同時達到了圖像的彩色顯示要求。

評論