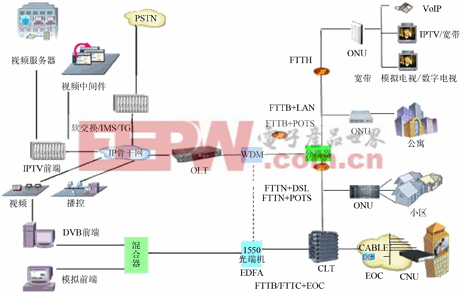

基于CN8980芯片組的HDSL2設(shè)備設(shè)計(jì)

關(guān)鍵詞: HDSL2;成幀器;EOC

美國Conexant公司的CN8980芯片組是功能強(qiáng)大的DSL收發(fā)器芯片,不但可以用于增強(qiáng)的基于2B1Q和CAP調(diào)制技術(shù)的第一代HDSL傳輸設(shè)計(jì),而且可以用于基于OPTIS調(diào)制技術(shù)的HDSL2傳輸系統(tǒng)的設(shè)計(jì),并且完全兼容HDSL2用于T1傳輸?shù)腁NSI標(biāo)準(zhǔn)和HDSL2用于E1傳輸?shù)腅TSI現(xiàn)有規(guī)定。它與現(xiàn)有HDSL設(shè)備保持良好的兼容性,利于已有HDSL系統(tǒng)的升級換代。

CN8980芯片組的結(jié)構(gòu)與特性

CN8980芯片組由兩部分組成:模擬部分和數(shù)字部分。

模擬部分

AFE和線路驅(qū)動(dòng)實(shí)現(xiàn)線路信號的傳送與接收功能,線路信號包含兩種模式:HDSL2 OPTIS和HDSL1 2B1Q。其功能模塊包含D/A和A/D變換,數(shù)據(jù)變換的反混疊(anti-aliasing),信號濾波,增益控制和線路驅(qū)動(dòng)。AFE由DSP收發(fā)器進(jìn)行控制。

數(shù)字部分

?可旁路的成幀器/映射器

成幀器/映射器是一個(gè)高性能的比特流處理引擎,可以處理任何HDSL幀結(jié)構(gòu),支持ANSI HDSL2 和ETSI HDSL1標(biāo)準(zhǔn)幀結(jié)構(gòu)。它進(jìn)行EOC(嵌入操作信道),和有效載荷比特的插入和提取,數(shù)據(jù)的加擾處理,比特填充,以及同步檢測。CN8980成幀器支持原始速率的T1/E1成幀和非幀模式,同步和異步有效載荷映射,以及每個(gè)時(shí)隙隨機(jī)或固定數(shù)據(jù)插入。此外,它還能夠進(jìn)行外部時(shí)隙增減控制,比特誤碼率測量,以及支持1、2、4、8比特時(shí)隙的可編程有效載荷映射。

?采用格柵編碼的速率自適應(yīng)比特泵DSP

速率自適應(yīng)DSP負(fù)責(zé)回波抵消,線路均衡和數(shù)據(jù)編碼。能夠進(jìn)行2、4、8、16電平PAM編碼,包含集成軟件控制的時(shí)鐘用于恢復(fù)和合成功能。DSP模塊中的發(fā)送器將從DSL成幀器處收到的數(shù)據(jù)映射成PAM編碼的符號,再經(jīng)格柵編碼和發(fā)送濾波處理后,發(fā)送到AFE。DSP模塊中的接收器接收來自AFE的串行數(shù)據(jù)和比特泵發(fā)送的經(jīng)過預(yù)編碼的符號,并將這些經(jīng)過預(yù)編碼的符號送到回波抵消器(EC)。回波抵消器對回波響應(yīng)進(jìn)行評估,并將AFE發(fā)來的信號減去回波響應(yīng)。回波處理后的信號還要通過前向均衡(FFE)和判定反饋均衡(DFE),最后再由格柵編碼調(diào)制(TCM)譯碼器恢復(fù)出信息比特。

圖1CN8980芯片組功能框圖

圖2系統(tǒng)基本框圖

圖3 PCM接口部分連接示意圖

圖4模擬前端芯片連接示意圖

?高性能微內(nèi)核處理器

片內(nèi)8051兼容微內(nèi)核處理器提供DSP控制和調(diào)度,另外也可以作為通用控制器對外部器件進(jìn)行控制,比如控制編解碼器或T1/E1成幀器以及與網(wǎng)絡(luò)管理軟件進(jìn)行通信等。

CN8980芯片組功能框圖如圖1所示。

在設(shè)備結(jié)構(gòu)上,CN 8980支持多信道線路卡。具有以下特性:單個(gè)啟動(dòng)ROM裝載;每個(gè)信道全自動(dòng)啟動(dòng)排序;每個(gè)高速PCM接口允許最大八個(gè)設(shè)備共享一條通用PCM總線;集成的成幀器支持每個(gè)信道的任意時(shí)隙分配;信號信道支持點(diǎn)到多點(diǎn)訓(xùn)練。

HDSL2系統(tǒng)總體方案的設(shè)計(jì)

方案采用單線對HDSL2配置,實(shí)現(xiàn)T1/E1數(shù)據(jù)傳輸,線路編碼為OPTIS技術(shù),采用片內(nèi)8051進(jìn)行系統(tǒng)控制。設(shè)計(jì)中充分考慮了未來的升級與設(shè)備擴(kuò)展,設(shè)計(jì)了多線對數(shù)據(jù)與控制接口及配置開關(guān),通過配置開關(guān)、軟件的改動(dòng)和外加控制即可實(shí)現(xiàn)系統(tǒng)的擴(kuò)展與升級。在保證對現(xiàn)有HDSL設(shè)備兼容的同時(shí),實(shí)現(xiàn)了先進(jìn)的HDSL2技術(shù)。系統(tǒng)基本框圖如圖2所示。

CN8980芯片組采用三芯片方案,即收發(fā)器(Zipwire2 Tranciever)、成幀器(Zipwire2 Framer)和模擬部分(Zipwire2 AFE)分別為一枚芯片。

系統(tǒng)有以下兩種工作模式:

?單板工作模式,支持1T1、1E1、和單線對可變速率,數(shù)據(jù)速率范圍可以為從144kbps到4624kbps之間,以16kbps為一級的任意速率,即成幀器支持的速率為N*64kbps+16kbps。

?多板工作模式,2塊到8塊系統(tǒng)電路板通過多板接口進(jìn)行連接,支持2T1、2E1和3E1 HDSL1配置,可以用于多端口設(shè)備和DSLAM設(shè)備。

系統(tǒng)各部分的設(shè)計(jì)

圖5 RS-232接口連接示意圖

圖6 HOST控制連接示意圖

圖7 主程序流程框圖、

PCM總線接口

PCM接口為DSL成幀器與其它標(biāo)準(zhǔn)T1、E1或N×64kbit設(shè)備的連接提供接口,采用Rockwell半導(dǎo)體系統(tǒng)公司的Bt8370芯片,支持T1/E1格式的數(shù)據(jù)收發(fā)。Bt8370與HDSL2成幀器之間的連接示意圖如圖3所示。

圖中CLADO、RSBCKI和RCKO是T1/E1接收時(shí)鐘,RPCMO是T1/E1接收數(shù)據(jù),RMSYNC是T1/E1接收復(fù)幀同步,TSBCKI和TCKI是T1/E1發(fā)送時(shí)鐘,TPCMI是T1/E1發(fā)送數(shù)據(jù),TMSYNC是T1/E1發(fā)送復(fù)幀同步。

模擬前端(AFE)部分

AFE對外提供數(shù)字接口和模擬接口。數(shù)字接口即DSP接口,與HDSL2收發(fā)器的DSP相連,用于數(shù)據(jù)傳輸。模擬接口由線路驅(qū)動(dòng)反饋電阻、阻抗匹配電阻、外部混合電路和變壓器組成,與雙絞線相連。

模擬前端部分是HDSL2收發(fā)器與銅雙絞線之間的接口,完成HDSL2數(shù)字信號與線路模擬信號之間的轉(zhuǎn)換,發(fā)送時(shí)提供足夠的線路發(fā)送功率,接收時(shí)完成初步的信號濾波等功能。HDSL2線路工作頻率較高,這部分的性能直接關(guān)系到系統(tǒng)傳輸性能的好壞。因此,這部分的設(shè)計(jì)非常關(guān)鍵,元件的選擇與電路的設(shè)計(jì)都有嚴(yán)格的要求。CN8980芯片組用單獨(dú)的一塊芯片完成模擬前端的功能,它與HDSL2收發(fā)器之間的連接示意圖如圖4。

圖中ser1_tx、ser2_tx是HDSL2發(fā)送數(shù)據(jù)信號,ser1_rcv、ser1_rcv,ser1_rcv為HDSL2接收數(shù)據(jù)信號,afe_clk,up_w_da等信號是HDSL2收發(fā)器對HDSL2模擬前端芯片的控制信號。

模擬前端比較重要的部分還包括混合電路和過擊保護(hù)電路,混合電路的目的是建立傳輸線路的阻抗模型,通過這個(gè)阻抗模型生成近似的傳輸信號回波,將線路變壓器上的信號減去這個(gè)近似回波就可得到一階接收信號的近似值。盡管CN8980內(nèi)部包含數(shù)字回波抵消器,但是混合電路減少了模數(shù)變換器(ADC)的輸入信號電平,有效地減少了短環(huán)路上的ADC溢出,增加了接收信號的量化分辨率,從而得到更好的信號處理性能。

系統(tǒng)中包含兩個(gè)混合電路,可以滿足較大范圍的環(huán)路特性和數(shù)據(jù)速率。兩個(gè)混合電路中一個(gè)用于高速率情況,一個(gè)用于低速率情況,在系統(tǒng)啟動(dòng)時(shí),軟件將檢測哪一個(gè)混合電路能夠提供最好的回波抵消性能,從而作出選擇。

這部分電路中變壓器的選擇也是一個(gè)值得特別注意的問題。線路變壓器實(shí)際上是一個(gè)高通濾波器,用于傳輸線路與電路板之間的直流隔離。CN8980要求變壓器的匝數(shù)比必須為5:1(線路側(cè):電路側(cè))。同時(shí)變壓器的一次電感值L是一個(gè)要求非常嚴(yán)格的參數(shù),如果電感值太高,濾波器的截止頻率將太低,CN8980的回波抵消器不能抵消回波的低頻成分和信號互調(diào)干擾;反之,如果L太小,截止頻率太高,一部分信號分量被濾除掉,將造成信噪比的降低。最后,變壓器的選擇還必須考慮回波損耗值,以盡可能的優(yōu)化系統(tǒng)性能。

在混合電路的設(shè)計(jì)中采用了NPO和具有低電解吸收率的電容,保證電路具有良好的線性特性和回波抵消性能。通過過擊保護(hù)電路的設(shè)計(jì),使系統(tǒng)具有良好的抗雷擊性能。

RS-232接口部分

系統(tǒng)中提供了兩路RS-232串行接口,接口驅(qū)動(dòng)芯片采用MAXIM公司的MAX233,接口為標(biāo)準(zhǔn)9針插頭。這一部分的電路設(shè)計(jì)簡圖如圖5所示。

第一路RS-232接口用于PC機(jī)或其他網(wǎng)絡(luò)終端與系統(tǒng)之間的通信,進(jìn)行網(wǎng)絡(luò)管理和系統(tǒng)調(diào)試等。數(shù)據(jù)傳輸采用異步模式:38400波特,一個(gè)開始比特,8個(gè)數(shù)據(jù)比特,一個(gè)終止比特,沒有校驗(yàn)。PC機(jī)對系統(tǒng)進(jìn)行控制時(shí),通過調(diào)用系統(tǒng)API命令實(shí)現(xiàn)。

第二路RS-232接口被定義為Group talk接口,用于多組CN8980芯片組同時(shí)工作時(shí)(如多線對工作模式和多電路板堆疊模式),主芯片組與從芯片組之間的通信,進(jìn)行控制或進(jìn)行程序的裝載等。同時(shí)這路信號提供了一個(gè)用于內(nèi)部底層軟件的調(diào)試接口。數(shù)據(jù)傳輸采用異步模式:115200波特,一個(gè)開始比特,8個(gè)數(shù)據(jù)比特,一個(gè)終止比特,沒有校驗(yàn)。

由于CN8980片內(nèi)CPU與仿真接口直接并聯(lián),為防止在系統(tǒng)調(diào)試時(shí)發(fā)生沖突,在發(fā)送數(shù)據(jù)線上設(shè)置了三態(tài)門,對片內(nèi)CPU與仿真接口進(jìn)行隔離。

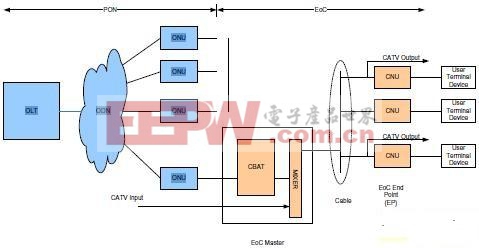

HOST端口

在多設(shè)備工作模式下,需要外部CPU對各個(gè)設(shè)備進(jìn)行協(xié)調(diào)控制,因此,在系統(tǒng)中設(shè)計(jì)了HOST端口,它直接與內(nèi)部HOST總線連接,通向片內(nèi)CPU。在開發(fā)、調(diào)試和測試外部CPU控制程序時(shí),使用HOST端口將非常方便。HOST端口與片內(nèi)CPU之間的通信通過HOST RAM實(shí)現(xiàn),在外部CPU對設(shè)備發(fā)出控制指令時(shí),將信號通過HOST端口寫入HOST RAM,產(chǎn)生中斷信號,由片內(nèi)CPU進(jìn)行處理,反之,HOST讀取片內(nèi)CPU寫入HOST RAM中的信息得到反饋信息。HOST CPU對設(shè)備的管理與控制采用API命令的方式進(jìn)行。

當(dāng)設(shè)備作為MASTER設(shè)備時(shí),其片內(nèi)CPU可以最多控制7臺SLAVE設(shè)備,可以將這8臺設(shè)備編為一組,由外部HOST CPU通過MASTER設(shè)備的HOST端口對這一組進(jìn)行控制管理,CN8980芯片組對HOST CPU能控制的設(shè)備數(shù)目沒有限制,因此通過這種方式,可以組成一個(gè)龐大的設(shè)備組,達(dá)到巨大的通信線對數(shù),非常適合作為局端設(shè)備。這種組網(wǎng)方式如圖6所示。

圖中,每一組的設(shè)備0為MASTER設(shè)備,與HOST總線相連,與HOST CPU進(jìn)行通信,設(shè)備1~設(shè)備7為SLAVE設(shè)備,通過Group talk接受MASTER設(shè)備的控制。

片外CPU/仿真接口

CN8980芯片內(nèi)部自帶8051CPU,但是可以通過跳線屏蔽掉,通過外部8051CPU/仿真接口使用板上的外部8051CPU,片外8051CPU/仿真接口也用作內(nèi)部8051CPU代碼的調(diào)試接口。

注意,這里的片外CPU和通過Host Port外接主CPU有所不同,這里的片外CPU使用需要屏蔽掉CN8980芯片組的內(nèi)部CPU,而Host Port外接主CPU使用時(shí),是通過API函數(shù)調(diào)用的方式對內(nèi)部CPU進(jìn)行操作,通過內(nèi)部對系統(tǒng)進(jìn)行控制,內(nèi)部CPU仍然是工作的。

系統(tǒng)軟件流程如圖7所示。

Boot Code State

CN8980芯片內(nèi)嵌8051CPU帶內(nèi)置256Byte直接和間接訪問RAM;2K不可編程ROM,內(nèi)部為系統(tǒng)初始化啟動(dòng)代碼;1KByte雙向HOST端口RAM,8KByte數(shù)據(jù)RAM,64KByte程序RAM(低端2KByte和不可編程ROM重疊,高端1KByte和HOST端口RAM重疊,因此是不可訪問的);由于系統(tǒng)的功能很多,并且片內(nèi)CPU要控制一些外部設(shè)備,程序量較大,并且考慮到系統(tǒng)的許多升級與擴(kuò)展只需要通過軟件的升級就可以實(shí)現(xiàn),為保證足夠的升級空間,因此系統(tǒng)中外加了1Mbyte的flash ROM和32Kbyte的RAM空間。

系統(tǒng)不同的工作和配置模式,采用的程序裝載進(jìn)入程序RAM內(nèi)的方式都不一樣,以保證系統(tǒng)的協(xié)調(diào)工作。主要包含以下方式:

?從外部flash裝入(MASTER設(shè)備)——每塊電路板只需要一塊flash ROM;

?通過HOST端口從外部CPU裝入(MASTER設(shè)備);

?通過RS232接口從外部HOST主機(jī)裝入(MASTER設(shè)備);

?通過Group talk接口從MASTER設(shè)備裝入(SLAVE設(shè)備);

HDSL2設(shè)備在將要執(zhí)行完啟動(dòng)片內(nèi)ROM中的代碼時(shí)將進(jìn)行程序的裝入,根據(jù)BOOTOP開關(guān)的設(shè)置設(shè)備選擇程序裝入的來源及裝入方式。MASTER可以通過設(shè)備內(nèi)FLASH、RS232接口、HOST端口進(jìn)行裝入,在裝載完成以后將根據(jù)BOOTOP開關(guān)的設(shè)置決定是否通過Group talk向SLAVE設(shè)備進(jìn)行裝載。SLAVE只能通過Group talk裝入。MASTER對SLAVE設(shè)備的程序裝載既可以采用廣播方式對所有的SLAVE同時(shí)進(jìn)行裝載,也可以一次只對特定的一臺設(shè)備進(jìn)行裝載。在裝載完后,操作碼將通過API命令對裝載進(jìn)行校驗(yàn),這時(shí)每臺設(shè)備都將進(jìn)行完全的自檢,片內(nèi)8051和外部HOST CPU都能進(jìn)行裝載校驗(yàn)過程,但是有所不同:片內(nèi)8051只能對一組設(shè)備(最多7臺設(shè)備)進(jìn)行校驗(yàn),而外部CPU能校驗(yàn)所有的設(shè)備組。

_DSL Initialization State

局端設(shè)備和遠(yuǎn)端設(shè)備都會進(jìn)行初始化,在初始化過程中,軟件對設(shè)備進(jìn)行缺省配制后進(jìn)入Out-of-Service Check state.

Out-Of-Service Check

CPU 查詢START[5:0]的狀態(tài)來決定程序是否進(jìn)入空閑狀態(tài),如果進(jìn)入空閑狀態(tài)則程序旁路HDSL2配置,并關(guān)閉DSL LOOP管理器。PCM收時(shí)鐘與發(fā)時(shí)鐘保持一致來驅(qū)動(dòng)PCM總線,HOST處理器將通過API命令對系統(tǒng)進(jìn)行設(shè)定。

Configure ZipWire2 State

CPU查詢START[5:0], BOOTOP, DIP 開關(guān)的狀態(tài)對HDSL2進(jìn)行配置。

Handle Test Mode States

CPU查詢START[5:0]的狀態(tài)來決定是否進(jìn)入自檢模式,如進(jìn)入自檢模式,則關(guān)閉DSL loop管理器和Activation State管理器。HOST處理器可通過API命令啟動(dòng)DSL loop管理器和Activation State管理器。

DSL Reset Check

如果程序不停啟動(dòng)DSL loop管理器和Activation State管理器,HOST處理器可通過API命令對設(shè)備進(jìn)行軟復(fù)位。

API Manager

API管理器是處理通過 Host Port/RS232/ Group Talk 接口送來的API命令的執(zhí)行機(jī)構(gòu)。外部HOST 處理器只能與Group Master通信,Group Master則通過Group Talk Serial Link協(xié)議轉(zhuǎn)發(fā)HOST 處理器的API命令到Group slaves或?qū)roup slaves的狀態(tài)轉(zhuǎn)發(fā)到HOST 處理器。

Bit-pump Manager

Bit-pump(比特泵)管理器負(fù)責(zé)系統(tǒng)訓(xùn)練過程,而且在正常操作中對溫度和環(huán)境變化進(jìn)行自適應(yīng)調(diào)整。

DSL Framer Manager

DSL Framer管理器負(fù)責(zé)保持DSL幀結(jié)構(gòu)和對系統(tǒng)性能進(jìn)行監(jiān)測。

DSL Loop Manager

DSL loop管理器負(fù)責(zé)對環(huán)路反轉(zhuǎn)和切換主環(huán)路,主環(huán)路是到達(dá)正常狀態(tài)的第一通道,如果主環(huán)路失效,DSL loop管理器自動(dòng)把下一條可用通路設(shè)為主環(huán)路。

結(jié)語

第二代高速數(shù)字用戶線技術(shù)(HDSL2)是一項(xiàng)最新的銅線接入技術(shù),其良好的頻譜兼容性、高速對稱的數(shù)據(jù)傳輸能力、較遠(yuǎn)的傳輸距離使其在惡劣環(huán)境條件下快速提供寬帶接入具有其它技術(shù)不可比擬的優(yōu)越性,可廣泛應(yīng)用于Internet和接入網(wǎng)或E1、T1傳輸?shù)阮I(lǐng)域,具有廣泛的應(yīng)用前景。■

參考文獻(xiàn)

1. HDSL2_Technology_ Overview_Whitepaper,Levelone Company, August 1999.

2. Zimmerman,HDSL2 Tutorial, PairGain Technologies, 1998.

3. CN8980_DataSheet Conexant Company, 1999.

評論