FPGA實現(xiàn)CAN總線通信節(jié)點設計

在項目的特殊環(huán)境要求下, CAN總線通信要求使用FPGA作為系統(tǒng)中的主控制器, 較之傳統(tǒng)設計使用的單片機, FPGA能夠在速度和體積上有更好的適應性。FPGA 一方面減少了電路板的復雜程度, 縮短了實現(xiàn)周期; 另一方面, 其豐富的資源、超高的性能和靈活的可編程性, 提高了整個設備的可靠性, 大大增強了電路板設計的靈活性和可擴展性。文中通過設計FPGA 的接口電路, 并利用Verilog語言來編程實現(xiàn)CAN節(jié)點之間的通信功能。

1 CAN 接口硬件設計

1.1 CAN 節(jié)點的系統(tǒng)構成

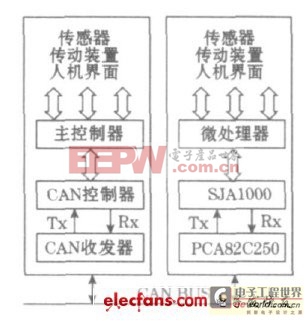

一般來說, 每個CAN 模塊能夠被分成3 個不同的功能塊,其結(jié)構如圖1所示。CAN總線收發(fā)器提供CAN協(xié)議控制器與物理總線之間的接口, 控制從CAN 控制器到總線物理層或相反的邏輯電平信號。它的性能決定了總線接口、總線終端、總線長度和節(jié)點數(shù), 是影響整個總線網(wǎng)絡通信性能的關鍵因素之一。CAN 控制器執(zhí)行在CAN 規(guī)范里規(guī)定的完整的CAN 協(xié)議, 它通常用于報文緩沖和驗收濾波, 對外具有與主控制器和總線收發(fā)器的接口。主控制器負責執(zhí)行應用的功能, 例如控制命令的發(fā)送、讀傳感器和處理人機接口等。它通過對CAN 控制器進行編程, 來控制CAN 總線的工作方式和工作狀態(tài), 以及進行數(shù)據(jù)的發(fā)送和接收。

圖1 CAN 模塊系統(tǒng)構成

1.2 接口電路設計

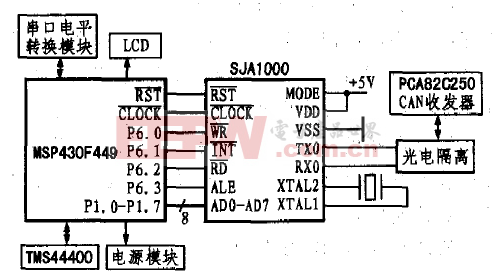

接口電路如圖2所示。SJA1000的AD0~ AD7地址數(shù)據(jù)復用端口、ALE地址鎖存端口、RD、WR、片選CS端口均通過轉(zhuǎn)換芯片與FPGA的I /O口相連。SJA1000 的中斷輸出信號INT連入FPGA, 使CAN通信可以采用中斷或查詢方式。RST 端口的電路實現(xiàn)SJA1000的上電自動復位功能。MODE 模式選擇端接+ 5 V, 設置SJA1000控制器為Intel模式。SJA1000 的時鐘晶振采用16MH z, 頻率調(diào)整電容取15 pF. R16為終端電阻,設計中取120Ω。 CAN 驅(qū)動器PCA82C250 的RS腳為工作模式選擇位, 接地工作于高速模式, 接高工作于待機模式。系統(tǒng)通過電阻R14將芯片設定于斜率控制模式, 電阻值為47 kΩ , 這時CAN 總線應工作于低速模式, 可提高CAN 總線抵抗射頻干擾的能力。在這種情況下, 可直接使用非屏蔽雙絞線作為總線。

設計中有2點需要特別注意: 第一點是FPGA 并沒有與SJA1000直接相連。這是因為對于設計選取的FPGAXCV600, 其接口電平不支持5 V TTL的I/O 標準, 如果與5 VI/O標準的SJA1000直接相連, 將可能導致FPGA 管腳電流過大, 造成器件鎖死或者燒毀。為此采用雙向總線收發(fā)器74ALVC164245, 把SJA1000的5 V TTL電平信號AD0 ~ AD7、

fpga相關文章:fpga是什么

通信相關文章:通信原理

晶振相關文章:晶振原理 雙絞線傳輸器相關文章:雙絞線傳輸器原理

評論