引領28nm FPGA“智”造時代

電子業的四大趨勢

本文引用地址:http://www.104case.com/article/236326.htm隨著我國政府“十二五”規劃的逐步推行,無線通信、新能源、集成電路、醫療保健等領域的技術創新倍受關注。為實現由“中國制造”向“中國創造”和“中國智造”的轉型與升級,新趨勢對電子產業提出了新的要求。

賽靈思(Xilinx)公司全球總裁兼CEO(首席執行官) Moshe Gavrielov認為,中國市場乃至全球范圍內,有四大趨勢是推動其業務不斷增長并將長期存在的市場發展因素。

第一,永不滿足的帶寬需求。尤其是智能手機、高清視頻等應用帶來的無線和有線通信領域信息流量的爆炸式增長。

第二,無處不在的連接計算需求。隨著信號處理、數據處理和基于IP的連接進入幾乎每一個我們可以想象的電子設備中,機對機通信對連接計算的需求越來越多。

第三,持續擴大的市場應用海洋。數以百萬計的新的消費者需要以低成本享受現代化的便利,低成本創新的市場因而加大。

第四,可編程勢在必行。成本因素正持續驅動著電子產業從ASIC/ASSP定制化及標準化設計,轉向前期NRE(非重復工程成本)成本可以忽略不計和風險較低的可編程平臺。

在這個連接能力無限強、嵌入式應用無限多、計算能力無限大的時代,是否有創新/“智”造的規律可循?

“上市時間”比“上市成本”更重要

在半導體業,通常認為,IC追求sooner,better,cheaper(更快、更好、更便宜)。在產業各個階段(上升期、成熟期和下降期),這三點的重要性不同。因此產品差異化的含義也不同。

但是作為一家“智”造公司,更快比更便宜重要。例如蘋果公司的商業模式之一是上市時間(Time to Market)比上市成本(Time to Cost)更重要。即誰先到市場,誰就有話語權。因為消費者已經接受了這個概念(包括價格),因此后來者價格不容易高過前者,只能更低。

因此第一個出來,往往利潤最高。并且第一個賣家決定了這類產品的價格。但是過去我們的觀念是“me too”(模仿)。不斷把價格壓低,幾年下來產品的利潤被榨干。

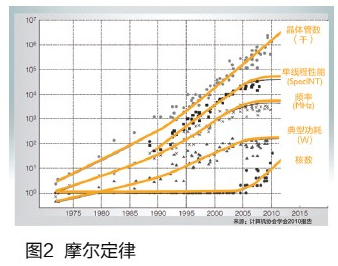

究其原因,摩爾定律(圖2)告訴我們,未來18個月,集成電路(IC)將集成更多的晶體管,因此在價格上會有更便宜的IC產品,會有更多的功能集成在IC中。

FPGA高利潤的奧秘

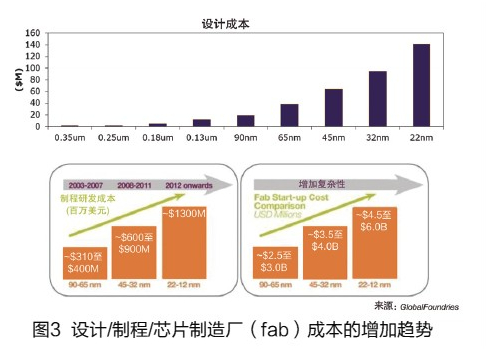

摩爾定律不僅為傳統的IC業提出了挑戰(晶體管密度和性能),更帶來NRE的挑戰。當IC制造的特征尺寸不斷縮小時,ASIC/ASSP(專用集成電路/專用用標準產品)的首次開工率在降低,取而代之的是FPGA(現場可編程邏輯器件)等可編程平臺的應用。這是因為可編程平臺具有靈活性高的突出特點,適用于廣泛的應用領域。隨著半導體制程技術向28nm的演進,使FPGA的功耗和制造成本都在大幅降低,相比之下,采用先進制程的ASIC/ASSP的成本卻在不斷提高(圖3),因此越來越多的新設計轉向FPGA平臺。

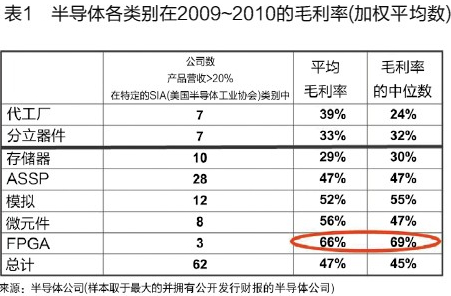

再轉到一個話題:當今哪類半導體利潤最高?通常認為是高性能模擬器件。但這兩年的調查令人難以置信,竟然是可以大批量制造的數字器件——FPGA(如表1)。

究其原因,EDA(電子設計自動化)工具廠商Mentor Graphics公司的董事長兼CEO(首席執行官)Walden C. Rhines分析認為,FPGA廠商的差異化做得好,因此更換FPGA供應商的難度最大!具體來看,體現在產品的差異化、基礎架構和生態環境等方面。產品差異化方面,FPGA廠商有高效的架構,具有法律約束(專利組合和版權),在每個工藝節點率先產品上市。基礎架構方面,不同供應商提供自己特殊的IP組合,用戶會對某些設計架構產生熟悉性和依賴性。生態環境方面,FPGA廠商都有專門的第三方IP開發者,獨立的應用支持和培訓教育體系。

既然FPGA有較高利潤,為何FPGA廠商的數量卻不多呢?賽靈思亞太區銷售及市場副總裁楊飛解釋為FPGA的門檻高:FPGA廠商和普通的IC廠商相比,軟件工程師的比例很大,例如賽靈思公司60%~70%的研發人員是從事軟件工作的。不僅用于支持芯片架構,還因為FPGA的應用場景多樣復雜,專家式的服務很重要。

FPGA的28nm創新

賽靈思的愿景是在當今的市場發展趨勢下,為中國系統工程師提供一個基礎創新平臺。為此,賽靈思在四大關鍵技術領域做了巨大的投入,誕生了四大關鍵技術創新:

● 28nm工藝;

● SSI(堆疊硅片互聯)技術;

● EPP平臺(可擴展處理平臺);

● 混合信號集成技術。

其中,28nm是所有新產品的制程基礎。

2011年10月24日,TSMC(臺灣積體電路制造股份有限公司)宣布已經開始為客戶量產使用28nm工藝的晶圓,相關的客戶包括有AMD, Altera, Nvidia, Qualcomm及Xilinx等。TSMC中國區業務發展副總經理羅鎮球2011年11月18日稱,其月產能已達12萬晶圓。

為了迎接28nm工藝時代,Xilinx早已未雨綢繆,此前于2011年3月發布了業界首款可擴展處理平臺(EPP)—ZYNQ嵌入式處理器,同月又全球首發了28nm高性能低功耗FPGA產品—Kintex-7,6月發布高性能FPGA產品—Virtex-7。在TSMC宣布量產28nm晶圓的第三天—10月26日,Xilinx宣布堆疊封裝產品(SSI)正式量產。

28nm FPGA助力中國“智”造

作為“十二五”規劃的一部分,我國正努力成為一個全球性的研發中心,并努力擴大內需及滿足全球市場的需求。

在當今時代,我們對芯片的要求將體現在以下兩個方面:平臺化,需要芯片和軟件兩部分,就像蓋房子一樣,研發人員可以用磚頭(芯片)和工程設備(開發工具)建造各種建筑;低功耗技術成為芯片設計中追求的最重要的指標,低功耗條件下的高性能需要芯片設計工程師在電路設計上精雕細琢,并且采用先進的半導體制程。

賽靈思一直注重軟硬件結合的產品推出,2008年推出了TDP(目標設計平臺),2011年又發布了基于28nm的系列FPGA產品,可以說為“智”造搭建了扎實的平臺,為工程師的靈感揮灑奠定了堅實的基礎。

28nm工藝的優勢

工藝挑戰

今年10月,TSMC(臺積電)宣布其先進的28nm工藝逐步實現量產,其中包括28nm高性能工藝(28HP)、28nm低功耗工藝(28LP)、28nm高性能低功耗工藝(28HPL)、以及28nm高性能移動運算工藝(28HPM)。在28nm方面,TSMC將同時提供高介電層/金屬柵(HKMG,High-k Metal Gate)及氮氧化硅(SiON)兩種材料選擇,與40nm工藝相較,柵密度更高、速度更快、功耗更少。之所以選擇跳過32nm,是因為工藝都是基于服務客戶的需求。相較于32nm,28nm的柵密度顯然高出許多。同時考慮到客戶在高性能應用中對于速度以及無線移動通訊對于低功耗方面的要求,分別推出以HKMG柵極工藝的28HP以及延續SiON柵極介電材料的28LP,相信會給客戶帶來更多在性能、功耗及成本方面的效益。

據TSMC負責研發的資深副總裁蔣尚義博士介紹,TSMC的HKMG用于28HP中的是全新的工藝,與40nm相較在相同漏電基礎上有50%的速度提升,相同速度基礎上漏電亦有大約50%的降低。盡管HKMG的工藝成本會增加,但是TSMC在每一代的工藝都會給客戶盡可能高的性價比。TSMC的28nm HKMG比一般32nm有更高的柵密度、更快的速度、更低的功耗,同時HKMG更進一步降低了柵極的漏電。

2010年,TSMC已為客戶的28nm FPGA提供了先進的硅穿孔(TSV, Through Silicon Via)以及硅中介層(Silicon Interposer)的芯片驗證(prototyping) 服務。憑借TSMC研發的TSV及與IC制造服務業者兼容的晶圓級封裝技術,TSMC承諾與客戶緊密合作開發符合成本效益的2.5D/3D(2.5維/3維)集成電路系統整合方案。

如果用一個簡單的量化標準來衡量28nm和40nm工藝的區別的話,集成度是傳統40nm工藝的兩倍。通過將更多功能單元集成在單一的系統級芯片上,企業可以大幅降低終端產品成本,并且可以制造出更小、更薄的產品。與傳統的40nm工藝相比,在指定速度下,28HPL的功耗最高可以減少一半(圖4),部分設計的待機功率更可以低至30%,而速度上最高可以有將近80%的提升。

賽靈思的全新FPGA就是基于TSV技術的28nm新產品,賽靈思亞太區銷售及市場副總裁楊飛坦言這得益于28nm工藝技術——28nm高性能低功耗工藝(28HPL)。賽靈思推出了統一的Virtex架構,將整體功耗降低一半且具有高容量(200萬邏輯單元)的7系列FPGA產品,不僅能實現出色的生產率,解決 ASIC 和 ASSP 等其他方法開發成本過高、過于復雜且不夠靈活的問題,使 FPGA 平臺能夠滿足日益多樣化的設計群體的需求。

設計挑戰

新工藝帶來新競爭優勢的同時,將許多設計和制造上的挑戰也帶給業界,為此,要求設計者與EDA(電子設計自動化)和晶圓廠之間保持良好的合作以應對全新的設計和制造挑戰。

談及SoC(系統級芯片)設計師在新的節點中將會遇到的工具和方法的轉變, Synopsys公司戰略聯盟總監Kevin Kranen認為,新節點面臨的挑戰各不相同:32nm和28nm的EDA工具需求相同,其所面臨的主要挑戰包括以下幾方面:

⒈由于SiON柵極介質厚度過薄難以控制,在降低柵極漏電和閾值變異性方面的挑戰;

⒉在193nm光刻基本限值下的挑戰;

⒊用于參數提取的新工藝拓撲結構建模方面的挑戰;

⒋管理參數異變性,尤其是在簽核期間異變性的挑戰。

賽靈思的楊飛承認,考慮到28nm時的掩膜成本比前一代工藝更高,同時賽靈思還要為芯片增加更多的性能和功能所帶來的芯片復雜度的提升、軟件效率的提升、更多的測試流程、開發更多的解決方案(賽靈思目標設計平臺,TDP),所以賽靈思在28nm節點的研發投入較其他企業會更高。但是,研發的高投入是可以通過更多的市場和應用來抵消掉。由于FPGA的可重新編程性,所以賽靈思不需要像ASIC/ASSP那樣針對細致化的市場或應用來開發方案。因此,掩膜和研發成本就可以在許多不同的應用和市場中攤銷掉了。最新的SSI技術(堆疊硅片互聯)可以有效地幫助賽靈思實現大型FPGA芯片的生產良率,從而降低成本并開發出大型FPGA。因此相信在28nm節點或者更先進的工藝上,FPGA是比ASIC和ASSP更具競爭優勢的。

在降低設計總成本方面,賽靈思和Synopsys合作采取并收到明顯效果的3項措施如下:

⒈提供合格的標準元件、內存和接口IP;

⒉預測試流程的優化;

⒊快速原型和FPGA。

賽靈思28nm工藝平臺產品家族

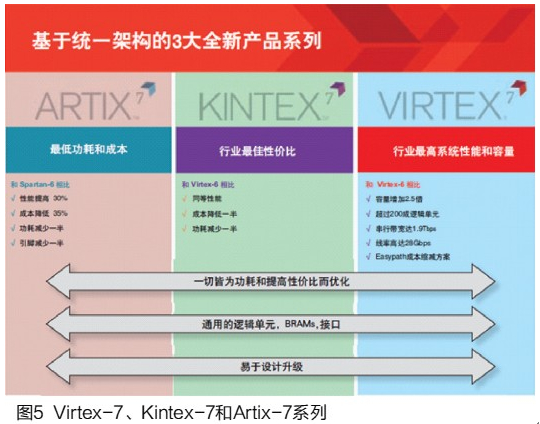

以Virtex為統一架構基礎,賽靈思將其28nm FPGA產品劃分三個系列:低端的Artix-7,中端的Kintex-7和高端的Virtex-7。相比于賽靈思之前的Virtex和Sparten兩大架構,7系列FPGA共享統一架構,并且采用TSMC高性能、低功耗(HPL)28nm工藝制造而成,具有優秀的可擴展性和高效的生產率,能夠在Artix-7、Kintex-7與Virtex-7 FPGA系列之間方便地進行移植,系統制造商能夠對成功設計方案輕松進行擴展,以滿足更低成本、更低功耗或更高性能的要求。

這三個系列將幫助賽靈思贏得更大的ASIC和ASSP市場份額,深入地打入從低功耗醫療設備到最高性能的有線和無線網絡設備更為廣闊的垂直市場。另外,在28nm工藝平臺之上,賽靈思還推出可擴展處理平臺的Zynq產品系列,并配合相應的ISE軟件開發環境。

三大產品系列

Kintex-7:低功耗及良好性價比

2011年3月,賽靈思全球第一款28nm產品——Kintex-7 325T FPGA發貨。

借助新的中端系列Kintex-7,賽靈思現在能夠為市場提供高性價比的FPGA產品。Kintex-7器件的性能比Artix-7 FPGA高40%,比Spartan-6快得多。Kintex-7系列器件的價格和功耗將是Virtex-6 FPGA的一半,但性能和功能等同。

Kintex-7器件特別受要求成本效益的信號處理應用的歡迎,是實施長期演進(LTE)無線射頻和基帶子系統的理想選擇。配合賽靈思近期發布的第四代部分可配置技術,7系列的用戶可以進一步降低功耗和成本,實現毫微微基站、微型基站和一般基站的廣泛部署。這些器件的串行連接性能、存儲性能和邏輯性能非常適合于大規模有線通信,比如把高速網絡帶到小區和每家每戶的10G無源光網絡(PON)光線路終端(OLT)線卡。

此外,Kintex-7 FPGA還適用于消費電子市場上的高清3D平板顯示器、用于新一代廣播視頻點播系統的互聯網視頻協議橋、軍用航電需要的高性能圖像處理系統和支持多達128個高分辨率信道的超聲設備。

Virtex-7:支持下一代高帶寬系統

2011年6月,Virtex-7的首款產品Virtex-7 485T面世。

Virtex-7 FPGA專門針對需要最高性能和最高帶寬連接功能的通信系統進行了精心優化,相對前代FPGA系統在容量翻番的同時,實現了30%的系統性能提升和50%的功耗下降。Virtex-7 FPGA 具有200萬個邏輯單元、85Mb內存、6.7Tb-MACS DSP吞吐量、2.8Tb/s串行帶寬以及完全集成的靈活混合信號功能,非常適用于最高性能的無線、有線、廣播基礎設備、航空航天與軍用系統、高性能計算以及ASIC原型設計與仿真應用領域。

Virtex-7系列由T、XT和HT器件組成,可滿足不同的市場需求。

Artix-7:低功耗和低成本

Artix-7預計2012年上半年面市。新系列Artix是英文arctic(北極)的諧音,象征著該產品將有極低功耗(熱量)。

作為入門級產品,新Artix-7系列具有最低的絕對功耗和成本,并采用小尺寸封裝,密度為20,000到355,000邏輯單元。該器件的價格比Spartan-6 FPGA低35%,速度快30%,功耗低50%。從Spartan-6 FPGA轉移到Artix-7器件,設計人員可以實現將靜態功耗降低85%并將動態功耗降低35%。

Zynq:可擴展處理平臺

賽靈思2011年3月推出了全球第一個可擴展處理平臺Zynq系列,為嵌入式領域注入了一股新鮮血液,徹底打破了傳統嵌入式處理器的性能瓶頸。

Zynq-7000產品系列,集基于ARM Cortex-A9 MPCore處理器的完整片上系統(SoC)和集成28nm可編程邏輯為一體,專為要求高處理性能的嵌入式系統而構建,其目標市場包括汽車駕駛員輔助、智能視頻監控、工業自動化、航空航天與軍用、廣播以及新一代無線應用等。

ISE 13提升效率

當今芯片的架構設計/平臺成為必然,包括芯片和軟件兩部分,軟硬結合是架構設計最主要的特征。因此,7系列的推出也伴隨著軟件開發環境的創新。

賽靈思ISE Design Suite 13設計套件,專門針對最新28nm 7系列FPGA,ISE 13致力于讓客戶最大限度地利用有限的時間和設計資源實現最大的生產力。

ISE 13在CORE Generator系統中提供了AXI(Advance extensible Interface,先進的可擴展接口)互聯支持,以構建性能更高的點對點架構。設計團隊如果構建了自己的符合AXI協議的IP(知識產權),那么就能利用可選的AXI BFM(總線功能模型)驗證IP仿真AXI互聯協議,從而可輕松確保所有接口處理都能正確運行。賽靈思ISE 13還為設計人員帶來了強大的PlanAhead設計環境和分析工具。

堆疊硅片互聯:FPGA邁向3D

超越摩爾定律

長期以來,摩爾定律因其驚人的準確性,成為半導體行業發展的準則和軌跡。但是,單單依靠摩爾定律,可控的功耗和代工廠良率無法滿足市場對資源無止境的需求。為此,賽靈思找到了一個新的思路—堆疊硅片互聯(SSI)技術,加上與伙伴合作的技術/工藝,使賽靈思成為挑戰3D(三維封裝)FPGA的先鋒,可以為市場推出一種能夠應對當下挑戰的可行的可編程解決方案。

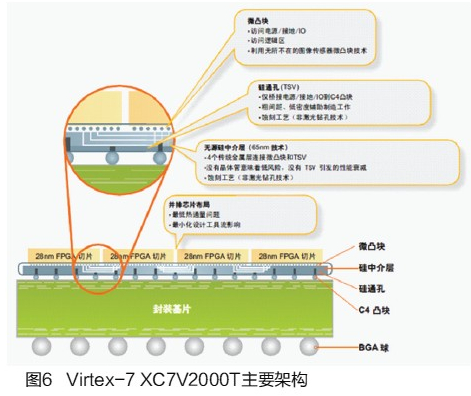

2011年10月,賽靈思橫空出世了堪稱世界最大容量FPGA—Virtex-7 XC7V2000T,為業界首批堆疊硅片架構的FPGA產品,其包含68億個晶體管,共200萬個邏輯單元(相當于2000萬個ASIC門)。據賽靈思公司全球高級副總裁、亞太區執行總裁湯立人介紹,Virtex-7 XC7V2000T不僅僅是晶體管數最大的FPGA產品,同時也是截至目前半導體歷史上集成晶體管數最多的單個IC—這不僅僅是摩爾定律的延續,更是對摩爾定律的超越。

因此,3D FPGA有望在一些領域內逐步取代ASIC和ASSP。湯立人稱,Virtex-7 2000T FPGA標志著賽靈思創新和行業協作史上的一個重大里程碑。對于客戶而言,其重大意義在于如果沒有SSI技術,至少要等演進到下一代工藝技術,才有可能在單個FPGA中實現如此大的晶體管容量。現在,有了Virtex-7 2000T FPGA,客戶能立即為現有設計增添新的功能,不必采用ASIC,單個FPGA解決方案就能達到3~5個FPGA解決方案的功能,因而可大幅降低成本。或者現在就可以開始采用賽靈思的最大容量FPGA進行原型設計和構建系統仿真器。這和通常的更新換代速度相比,至少可以提前一年時間。

SSI技術

新的SSI技術使賽靈思能夠為當代工藝技術帶來下一代的高密度性能,有望改善容量和集成度,節約PCB(印制電路板)板級空間,進一步提高產量。Virtex-7 XC7V2000T主要架構如圖6所示。

1. FPGA核心

最上層為FPGA核心層,采用4個含50萬邏輯單元的28nm FPGA核心(切片)肩并肩排布,而非采用2個含100萬邏輯單元的或單個200萬邏輯單元的FPGA核心。原因在于當IC的規模和復雜度不斷提升的同時,其良品率將受到一定程度的影響。此種設計能在保證良品率的同時,提高邏輯單元數目。

2. 微凸塊

微凸塊并非直接連接于封裝,而是互聯到SSI技術最關鍵的部分——無源硅中介層,進而連接到相鄰的芯片。這種設置方法能夠避免微凸塊受到靜電放電的影響,從而帶來巨大優勢。通過芯片彼此相鄰,并連接至球形柵格陣列,該器件避免了采用單純的垂直硅片堆疊方法出現的熱通量、信號完整性和設計工具流問題。

3. 硅中介層

SSI技術設置了一個65nm工藝的無源硅中介層,其本質類似于IC內部的互連線,在芯片外部實現了芯片間的直接互聯。這樣解決了傳統方式所帶來的問題,將單位功耗芯片間連接帶寬提升了100倍以上,時延減至五分之一,也不會占用任何高速串行或并行I/O資源。而且,硅片中的芯片連接數量大大超過系統級封裝。而且這種方法的最大優勢還在于節能性。通過SSI技術連接芯片,其功耗遠遠低于通過大線跡、封裝或電路板連接的方式。

fpga相關文章:fpga是什么

晶體管相關文章:晶體管工作原理

晶體管相關文章:晶體管原理

評論