基于ARM的石英晶體測試系統中DDS信號源設計

4 DDS掃頻輸出控制

本文引用地址:http://www.104case.com/article/235994.htm系統對DDS信號源設計的核心是控制產生0~100 MHz掃頻信號,信號的質量直接決定測試精度。由于采用溫度補償晶振給AD9852提供50 MHz參考頻率信號,因為AD9852產生的正弦信號是用于測試石英晶體參數的,所以對其參考頻率信號穩定度要求嚴格,TXC0(ROJON)型溫度補償晶振頻率負載波動±10%時,穩定度最大為±0.1×10-6,滿足系統精度需求。根據AD9852的文檔得到其輸出的最大頻率為

式中,fc為AD9852內部參考頻率;fmax為DDS最大輸出頻率。fc可以通過AD9852地址為0x1e的寄存器4倍頻,所以輸出正弦波最大頻率為100 MHz。測試時,先通過上位機或鍵盤輸入測試晶體的標稱頻率及掃描步進,然后以標稱頻率為中心設置適當的起始掃描頻率及終止掃描頻率。假設一個步進對應的頻率控制字為DFTW,則每個步進頻率

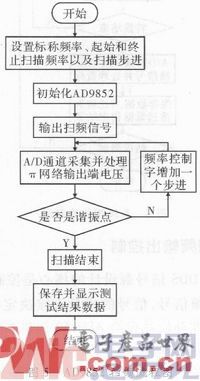

假設步進為1 kHz,則DFTW=0x53e2d623。AD9852進行掃頻輸出前,首先通過鍵盤或串口設置石英晶體的標稱頻率、起始和終止頻率、掃描步進頻率,STM32F103ZET6初始化AD9852后,按設定參數輸出相應掃頻信號,掃頻信號經過濾波、放大、跟隨等信號調理電路進入π網絡,π網絡輸出信號經過放大限幅處理后反饋到STM32F103ZET6的12位A/D輸入端,在采集數據經過中值濾波去除毛刺處理后保存數據并比較判斷是否為諧振點,如果不是,諧振點將頻率控制字FTW會加上一個步進頻率控制字DFTW,如此直到掃描到終止頻率為止,找出諧振頻率,最后根據公式算出石英晶體的諧振電阻。流程圖如圖5所示。

5 結束語

針對石英晶體參數測試系統,介紹了利用STM32F103ZET6控制AD9852作為信號源的方法。這種方法結合了傳統PC機及普通單片機測試系統的優點,避開了前兩者的缺點,可以快速地測試石英晶體電參數。通過實驗測試頻率控制在0~50 MHz時,測量的頻率與平均測量值的相對偏差為<0.5×10-6,在此區間測量得到的石英晶體串聯諧振頻率精度在2×10-6以內,基本滿足系統設計要求。如果增加DDS參考頻率信號的穩定度以及提高信號調理電路的抗干擾能力,可大幅提高石英晶體串聯諧振頻率、串聯諧振電阻的精度,將對石英晶體電參數測試系統的應用具有重大意義。

評論