一款基于FPGA的I2C總線的設計方案

異步時鐘域的轉換,采用兩級寄存器的結構。輸入濾波器采用5 級寄存器的結構。當采樣到連續5 個高電平時,輸出才為高電平,否則為低電平。接口部分的寄存器全都用FPGA 的系統時鐘驅動。

本文引用地址:http://www.104case.com/article/234978.htm2.2 I2C SLAVE 控制邏輯的實現

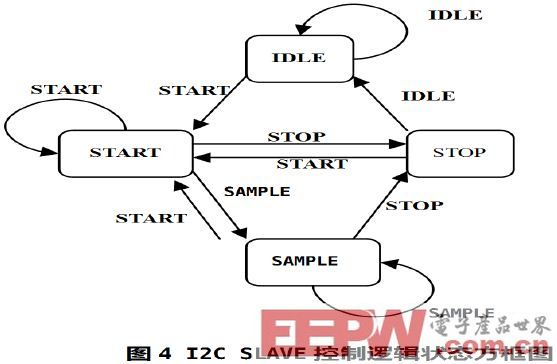

I2C SLAVE 控制邏輯狀態機是整個模塊的核心,所有I2C 總線相應的控制都由其完成。狀態機有四個狀態:IDLE,START,SAMPLE 和STOP 組成。Verilog 的定義如下:

`define IDLE 2'b00

`define START 2'b01

`define STOP 2'b10

`define SAMPLE 2'b11

下面介紹各個狀態的功能。當I2C 總線無任何操作時控制器在IDLE 狀態下,并保持。當接口邏輯判斷到START 條件時,控制器跳轉到START 狀態下,并做好接受第一個字節的準備,包括初始化bit計數器。接著開始接受第一個字節包含7bit的地址和1bit 的讀寫狀態位。當采集完第一個字節后,控制器跳到SAMPLE 狀態下,開始執行數據字節的接受或發送。是接受或發送的狀態由前一字節的最后1bit 的讀寫狀態位決定。

當讀寫狀態位為高時,表示I2C 總線的讀操作,FPGA 邏輯發送數據。讀寫狀態位為低時,表示I2C 總線的寫讀操作,FPGA邏輯接受數據。接著FPGA 邏輯發出一個ACK 信號后,表示可以進行讀寫操作。那么就進入到SAMPLE 狀態下,正常讀或寫一個字節(也可以連續的讀寫多個字節,對此沒有限制)。在完成8bit 數據讀寫后,I2C 的主器件會發出一個STOP 條件操作。fpga 邏輯收到后,就跳轉到STOP 狀態,并在幾個時鐘周期后,自動跳轉到IDLE 狀態下。從而完成一個完整的I2C 總線的讀或寫操作。

當然也包括一些異常處理,以防止狀態機處在一個不確定的狀態下。在SAMPLE 狀態下如果遇到意外的START 條件時,即上次的總線操作沒有完成就開始了下次的操作,則控制狀態機會跳轉到START 狀態下,而開始接受這次新的總線操作,而上次的操作為無效。由如在SAMPLE 狀態下,但是又收到一個START 條件。還有如在STOP 狀態收到一個START 條件,處理也和上面一樣。下圖4 介紹了I2C SLAVE 控制邏輯狀態機的狀態跳轉圖。

如上圖所示,在 SAMPLE 狀態下,可以連續的讀寫數據,而地址是在讀寫完一個字節后由FPGA 邏輯自動加1 的。這樣做使得I2C 總線的一次操作就可以連續對多個字節讀或寫。提高的總線的使用效率。

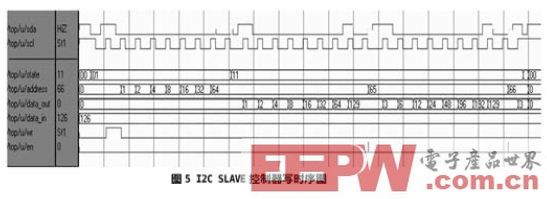

以下是在modelsim6.0 下進行的行為級仿真的時序圖。

由自行編制的I2C 總線主器件BFM 驅動進行測試。圖5 I2CSLAVE 控制器寫時序圖。圖6 I2C SLAVE 控制器讀時序圖。

3 結論

本方案通過介紹SLAVE 模式的特點,給出設計的原理框圖和modelsim 下的行為仿真時序圖。在Altera 的Cyclone II 系列中用Quartus II 12.0生成的模塊時鐘頻率可達到180MHz,占用的資源Totalcombinational functions 為83 個,Total registers 為41 個。而在實際應用中達100MHz 左右。證實了本方案操作簡便,效果不錯。

上拉電阻相關文章:上拉電阻原理

評論