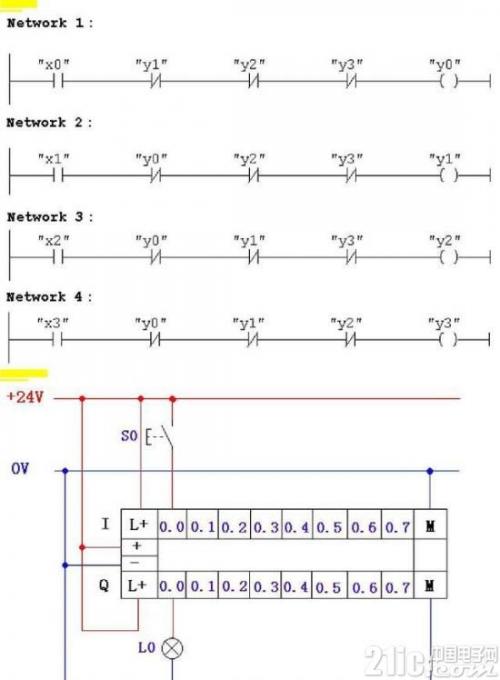

簡述控制驅動法的實現

圖6 VR預鎖存波形

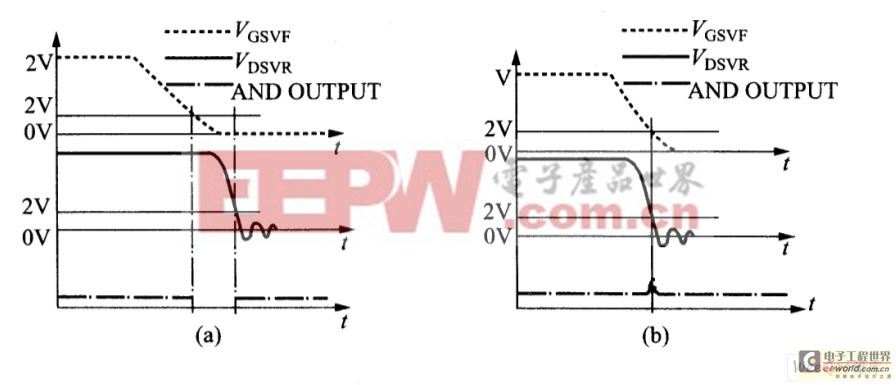

一個輸出起始設置在零的計數器控制著關斷電路。采用將計數器輸出全部設置為0,也即在PWM控制信號的下降沿及QF的柵源電壓之間實際上為零延時,結果QF的柵源電壓,VR的漏源電壓以及與門輸出的三個波形示于圖7(a)。

圖7 VF的關斷波形

(a)非最佳延遲(b)最佳延遲

VF關斷電路中的與門更多的作用如VR開啟控制電路中的或門,給一個命令到計數器,以直接令計數器向上或向下記數。在VF的關斷電路的情況,一個高電平從與門直達計數器以便在下個周期中向上記數。當計數器為下個周期增加一個記數值,則PWM控制器的下降沿與VF的柵源電壓之間的延遲就會增加,從與門的輸出脈沖就會變窄,這個反饋影響將持續到VF的柵源電壓和VR的漏源電壓能夠同步。當延遲最佳化時,波形示于圖7(b)。

如在VR控制執行電路中所描述,電路將會在兩個延遲值之間抖動,一個是最佳值,而另一個比最佳值略長一些。

評論