基于FPGA的數(shù)字存儲示波器的顯示技術(shù)

1 引言

由于液晶顯示器(LCD)功耗低,體積小,超薄,重量輕,而且車身沒有畫面幾何圖形的失真及收斂性誤差,也就投有了傳統(tǒng)顯示器中心和邊角出現(xiàn)色差和失真的問題,因而得到廣泛的運用。現(xiàn)場可編程門陣列(FP—GA)芯片具有高密度、小型化、低功耗和設(shè)計靈括方便等優(yōu)點,可以縮短研發(fā)周期,提高工作效率,因而在數(shù)字電路設(shè)計中得到了廣泛的應(yīng)用。作為人機交互的LCD在數(shù)字存儲示波器中有著重要的位置。在以往的設(shè)計中多采用液晶顯示專用芯片去驅(qū)動LCD.宴踐中發(fā)現(xiàn)它不但占用CPU資源,而且它與LCD數(shù)據(jù)接口之間存在干擾。為了解決這些問題.本文提出了.一種新的顯示技術(shù)。

2 總體設(shè)計方案

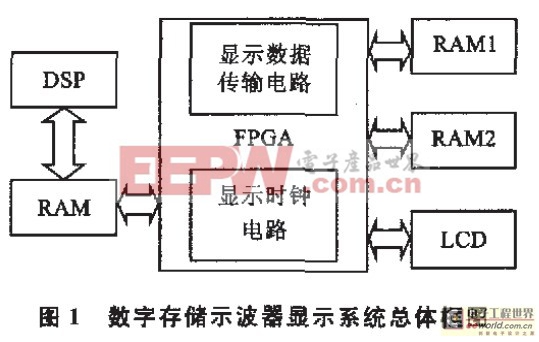

由于數(shù)字存儲示渡器對顯示的實時性和刷新率都要求較高,而且它顯示的大多是一些簡單的圖形和波形,因而直接用FPGA產(chǎn)生LCD所需的顯示控制時序。存放顯示數(shù)據(jù)的SRAM地址也直接由FPGA地址計數(shù)器產(chǎn)生。其顯示系統(tǒng)總體框圖如圖1所示。

在圖1中,A/U采集的數(shù)據(jù)經(jīng)DSP處理,轉(zhuǎn)換為LCD可以顯示的點陣數(shù)據(jù)后再存儲到RAM中}兩片顯示存儲器RAMl和RAM2交替讀取RAM中的數(shù)據(jù),最后送到I。CD上顯示。在FPC-A中設(shè)計了LCD顯示時鐘電路模塊和顯示數(shù)據(jù)傳輸電路模塊。顯示時鐘電路產(chǎn)生LCD顯示所需的各種時序;顯示數(shù)據(jù)傳輸電路設(shè)計兩路數(shù)據(jù)傳輸通道,RAM中的數(shù)據(jù)通過數(shù)據(jù)傳輸通道送到RAM1或RAM2中,再由LCD讀取RAMl或RAM2中的數(shù)據(jù)顯示。

對LCD及顯示存儲RAM的控制都由FPGA完成。

3 數(shù)據(jù)通道控制及實現(xiàn)

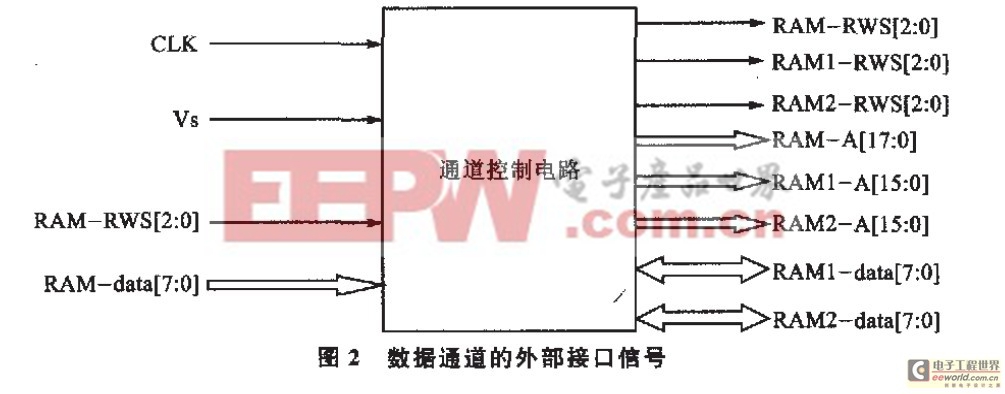

數(shù)據(jù)通道對存儲RAM的讀/寫操作進行控制,保證數(shù)據(jù)正確地從RAM傳送到RAMl或RAM2中,并能在LCD上正確地顯示。圖2為數(shù)據(jù)通道的外部接口信號。

圖2中,CLK為系統(tǒng)時鐘,Vs為DSP提供的時鐘;RAM—RWS[2:0]、RAM1一RWS[2 : 0]和RAM2一RWS[2:0]分別為RAM、RAMl和RAM2的讀/寫及片選信號;RAM—data[7:0]、RAMl一data[7:0]和RAM2一data[7 :0]分別為RAM、RAMl和RAM2的數(shù)據(jù)總線RAM—A[1 7:o]、RAMl一A[15:03和RAM2一All5:03為數(shù)據(jù)總線。由于采用了兩片RAM作為顯示存儲器,它們可依次向液晶提供顯示數(shù)據(jù),這樣,對每片顯示RAM的讀操作和寫操作分開,避免了因為數(shù)據(jù)的改寫而導(dǎo)致顯示的小穩(wěn)定。圖3為顯示RAM的工作時序圖,圖中Views為Vs反相后經(jīng)二分頻得到。

圖3顯示RAM工作時序

圈4顯示RAM的地址總線選擇電路原理圈數(shù)字存儲示渡器的顯示包括兩部分:一部分是界面顯示,包括菜單和光標(biāo)的顯示等;另一部分是波形顯示。

波形是隨時在更新,而菜單只有在按鍵操作的情況下才會改變,更新的次數(shù)很少。所以采用了分頁顯示技術(shù),即將顯示存儲空問分成兩個區(qū)間:一個區(qū)間用來存儲菜單、光標(biāo)等不常刷新的數(shù)據(jù);另一個區(qū)間用來存儲波形數(shù)據(jù)。每個區(qū)間都是一屏顯示所需的空間。LCD顯示時將兩個存儲區(qū)間里對應(yīng)地址的數(shù)據(jù)通過FPGA內(nèi)建電路相“或”以后再送LCD箍示。這樣在軟件處理時節(jié)省了重復(fù)刷屏的時間,同時簡化了軟件的編寫。

4 顯示時序電路設(shè)計

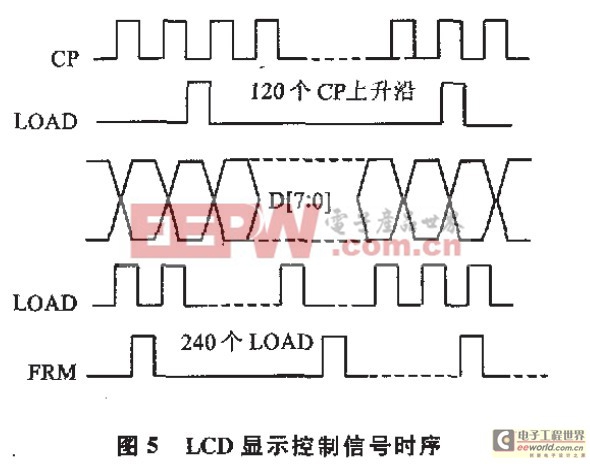

彩色液晶顯示器(采用NANYA公司的LCBFBLB61V4)有3根控制信號:CP、LOAD和FRM信號。其中,CP為移位脈沖信號,每來一個移位脈沖信號,LCD就從數(shù)據(jù)線上讀取顯示數(shù)據(jù)。LOAD為行裝載信號,當(dāng)LeD讀取一行數(shù)據(jù)后,會產(chǎn)生一個LOAD信號,將數(shù)據(jù)鎖存起來。FP,M為場同步信號.每顯示一屏數(shù)據(jù)就會產(chǎn)生一個FRM信號。彩色液晶的每個像素點的顯示狀態(tài)由3位數(shù)據(jù)的邏輯電平表示,因此顯示一行需320×3/8=120個cP時鐘,而3根信號線之間的關(guān)系為:LOAD的頻率是cP的120分頻,F(xiàn)RM的頻率是LOAD的240分頻。I.CD要求的顯示控制時序如圖5所示。

圖5中各顯示控制信號在FPGA中通過分頻器實現(xiàn):100 MHz系統(tǒng)時鐘32分頻得到3.125 MHz的移位圖4為顯示RAM的地址總線選擇電路原理圖。圖中A1[15:0]為LCD顯示RAM的讀地址,A2[15:0]為顯示RAM的寫地址,它們分別由硬件時鐘產(chǎn)生的地址計數(shù)器的輸出線。Views為多路選擇器的選擇信號,其工作原理為:當(dāng)Vs為低電平時,DSP占用RAM總線,RAM的地址總線由DSP的地址總線產(chǎn)生,DSP把處理后的數(shù)據(jù)送到RAM中;當(dāng)Vs為高電平時RAM自動執(zhí)行讀操作,其讀地址在FPGA中由硬件時鐘地址計數(shù)器產(chǎn)生,即自動把RAM中的數(shù)據(jù)送到RAMl或RAM2中;當(dāng)Views為高電平時,RAM中的數(shù)據(jù)送到RAMl中,此時RAM2中的數(shù)據(jù)送到LCD中擊顯示,當(dāng)VJews為低電平對,RAM中的數(shù)據(jù)送虱RAM2中,此時RAMl中的數(shù)據(jù)送到LCD中去顯示。當(dāng)然在FPGA設(shè)計中還應(yīng)包括存儲器的讀/寫、片選電路和地址譯碼電路等,這里不再詳述。

脈沖信號CP,再將CP信號120分頻得到行裝載信號LOAD.最后將LOAD進行240分頻得場同步信號FRM。

5 結(jié)束語

本文所介紹的示波器顯示技術(shù)已成功地運用于100 MHz數(shù)字存儲示波器中。該設(shè)計能高效、可靠地實現(xiàn)數(shù)據(jù)的傳輸及波形的重現(xiàn),提高了系統(tǒng)的抗干擾能力,降低了成本;并且該結(jié)構(gòu)具有很好的可移植性,只須做很少的改動就可應(yīng)用于不同的系統(tǒng)中。

評論