數(shù)字電源UCD9224與UCD7232應(yīng)用中輸出電壓關(guān)機負過沖的分析及解決

綜合上述信息可知,常規(guī)供電架構(gòu)設(shè)計中,空載關(guān)機時的輸出電壓負過沖依然是由于 SRE_1A和SRE_1B進入了高阻態(tài)導(dǎo)致。為消除該負過沖,同樣可以在SRE_1A和SRE_1B引腳添加下拉電阻來完成。

5.3 其它規(guī)避措施

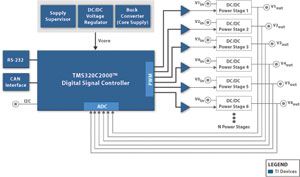

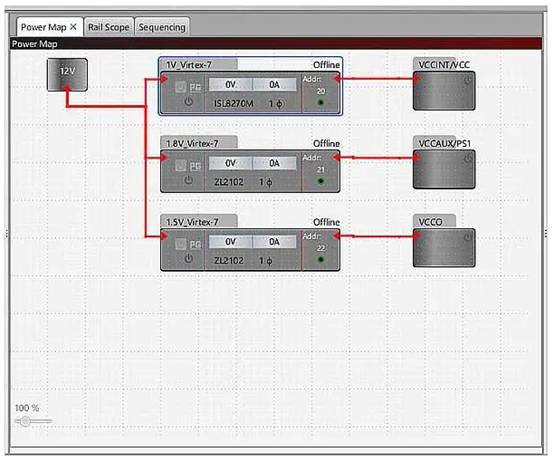

在關(guān)機動作發(fā)生后,12V電壓逐漸下降,會首先觸發(fā)欠壓保護(欠壓保護點由軟件設(shè)置),系統(tǒng)關(guān)機,DPWM和SRE被拉低,輸出關(guān)閉;隨著12V的繼續(xù)下降,觸發(fā)UCD7232的欠壓保護,F(xiàn)LT引腳變?yōu)楦撸⑸蠄蠼oUCD9224。圖13完整的顯示了上述過程。(圖13的CH4為3.3V電壓波形,CH3為SRE_1B引腳信號,CH1為FLT引腳信號)

由該波形可知,SRE_1B再次上升時,由于UCD7232還處于正常工作狀態(tài)(FLT還為低),因此BUCK下管可以正常導(dǎo)通,造成輸出電壓的負過沖。如果將系統(tǒng)欠壓保護點設(shè)置的略低一些,或減緩3.3V的下降速度,以保證UCD9224進入reset模式時,UCD7232已經(jīng)處于欠壓保護狀態(tài),則輸出電壓的負過沖亦可以避免。

圖 13:SRE_1B 與 FLT

為減緩3.3V的下降速度,可使用Dropout電壓較小的LDO,如TPS79333(VDROPOUT=0.18V)。由圖11和圖12對比可知,當前方案下使用的LDO具有較大的Dropout 電壓(6.9V-2.6V=4.3V)。如使用TPS79333,當UCD7232觸發(fā)4.1V欠壓保護停止工作時,UCD9224仍能得到穩(wěn)定的3.3V供電,也就避免了進入reset模式。

6. 結(jié)論

在只關(guān)閉3.3V的應(yīng)用場景中,輸出端無論是否帶載,輸出電壓都會出現(xiàn)負過沖;而在采用常規(guī)供電設(shè)計的系統(tǒng)中,關(guān)閉12V時,如果輸出端空載,同樣會出現(xiàn)負過沖問題。輸出電壓負過沖的根因是UCD9224在處于reset模式后,SRE_1A和SRE_1B引腳變?yōu)楦咦钁B(tài),其電壓有反彈并下降緩慢導(dǎo)致。解決措施是在SRE_1A和SRE_1B引腳各增加一顆下拉電阻。實測發(fā)現(xiàn),該解決措施簡單有效。

評論