時域反射儀的硬件設計與實現----關鍵電路設計(一)

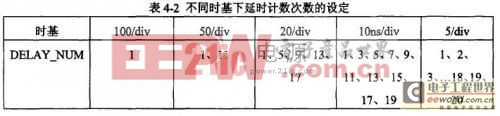

在表4-1中已經介紹過,在不同時基情況下,延時時間△t各不相同,最小延時間隔為0.2ns(5ns/div),最大延時間隔為2ns(50ns/div),因此隨著時基的變化,延時間隔和采樣次數都相應會不同。表4-2給出了在不同時基下延時間隔的設定。

3.1.3脈沖信號放大和分離

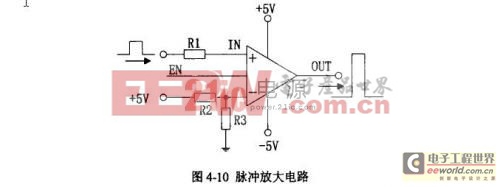

3.1.3.1脈沖信號放大

從FPGA的I/O口送出的脈沖信號,如果直接送到被測電纜上,測量效果必定會很差,首先因為FPGA的I/O引腳輸出電流不大,導致驅動能力(帶載)不足,同時由于FPGA的供電電壓為+3.3V,則使I/O口的輸出脈沖幅度最大只有+3.3V,如此小的電壓幅度以及低的帶載能力,被送到電纜后,由于電纜損耗的原因,觀測到的反射脈沖幅度可能會很小,影響測量準確度。為了改善以上不足之處,就必須對脈沖信號進行放大處理,以增強脈沖信號的帶負載能力,同時提高脈沖信號輸出幅度。

對脈沖信號的放大必須要保證脈沖信號的完整性,不能將脈沖信號放大后,輸出的脈沖信號與輸入信號相比發生了較大的失真,比如上升沿特性變差等。為此本設計選用了TI公司寬帶高速運放OPA691,該運放具有以下優良特性:

靈活的電源供電范圍:﹢5V~+12V(單電源)、±2.5V~±6V(雙電源)。

單位增益下的帶寬(Bandwidth)為:280MHz(G=l)

高輸出電流:190mA

輸出電壓范圍:±4.0V

高壓擺率(slew rate):2100V/us

低電源電流:5.lmA

關斷模式下電流:150uA

利用OPA691設計的脈沖信號放大電路如圖4一10所示。

評論