時域反射儀的硬件設計與實現----關鍵電路設計(一)

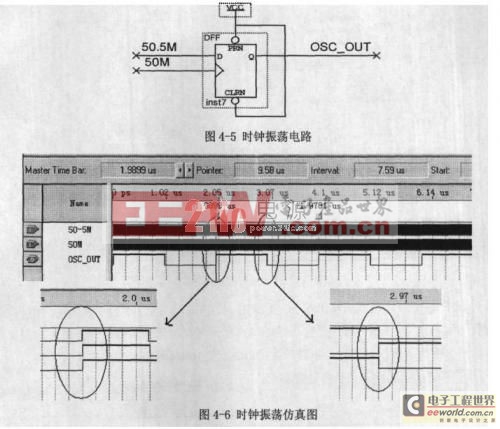

為了完成順序延時的目的,必須確定50M和50.5M的時鐘信號在什么時候才能同相對齊,通過圖今4可以看到,當兩時鐘信號對齊以后,根據兩者的周期差的原理,50M的時鐘信號的1號位置的上升沿必定對應了50.5M時鐘信號的高電平,而在同相對齊之前的一個時鐘,即50M時鐘信號的98號位置的上升沿必定對應50.5M時鐘信號的低電平。根據這一推理,可以利用D觸發器的原理,將50M時鐘信號作為觸發時鐘信號,將50.5M時鐘信號作為被觸發信號,則當兩時鐘信號剛好達到同相對齊時,D觸發器的輸出端從低電平變成高電平;當兩時鐘信號剛好達到反相對齊時,D觸發器的輸出端則從高電平變成低電平。D觸發器輸出呈周期變化,周期T=20ns*99=1.980us,約為50OKHz的周期信號。該設計方法形同一個振蕩電路,兩時鐘信號是振蕩源。OSC_OUT作為振蕩輸出信號,上升沿表示同相對齊,下降沿表示反相對齊。設計結構和時序仿真結果如圖4-5和4-6所示。

從圖4一6可以看到,振蕩輸出信號的周期為1.9781us,與前面計算結果基本保持一致

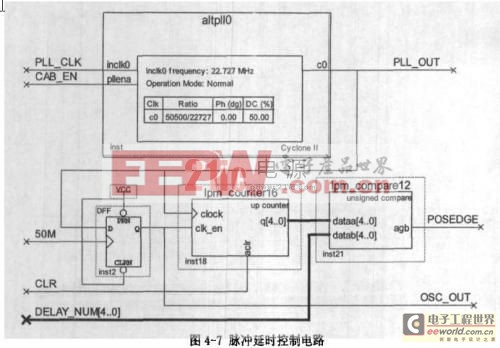

確定兩個時鐘信號的同相對齊點后,即可以實現步進延時的目的。由圖4-4己知,要實現0.2ns的延時,就可以在對齊之后,通過對50.5M時鐘信號進行計數,計數值為N,即被延時了0.2*N的時間間隔。為此可將圖4-5中的D觸發器的輸出端作為計數器的使能控制信號,當D觸發器的輸出端由低電平向高電平變化時,計數器開始對50.5M的時鐘信號計數,計數輸出結果與預設次數做比較,當相等時,則表示達到預設的延時效果,此時比較器的輸出狀態即可被認為是輸出脈沖信號的上升沿。脈沖延時控制電路如圖4一7所示。

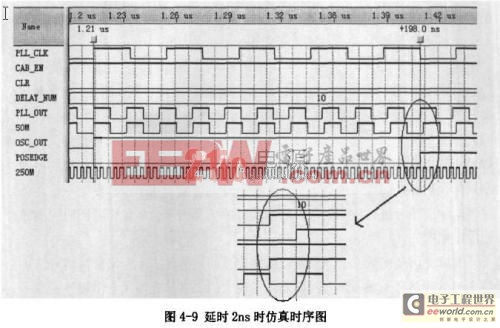

在圖4-7中,比較器的輸出端POSEDGE對應了圖4-1脈沖產生電路中的D觸發器的輸入信號,從D觸發器輸出端即可產生時域反射測量所需的脈沖信號。圖4-8、4-9給出了脈沖延時控制電路產生的0.2ns和2ns延時情況下的仿真時序圖。

評論