時域反射儀的硬件設計與實現----關鍵電路設計(三)

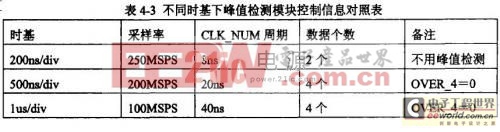

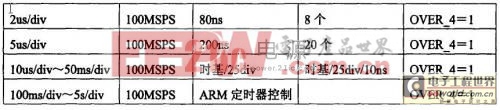

從表中可以看到,在一般情況下,CLK_NUM的周期都可以直接通過分頻來獲得,而在時基比較大時,如100ms/div情況下,由于本設計的存儲深度在3K左右,對應了10屏(每屏300個點)的圖形,如果一次連續的將存儲器填滿,則需要的時間大概為12s,信號刷新率太低,不適合波形顯示,因此在100ms/div時基以后,都采用了軟件采樣的方式,且此時沒有存儲深度的概念。波形顯示采用了掃描的方式,CLK_NUM的周期由ARM內部的定時中斷器開控制。此時屏幕上的信號不是一次刷新,而是從屏幕左方向右方依次更新,當更新完最后一列信號后,又重新回到屏幕波形顯示區域的最左側,依次顯示新的波形。

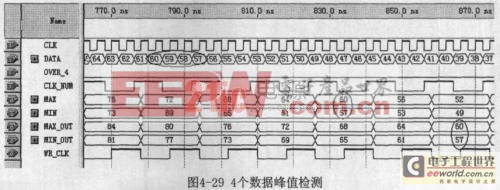

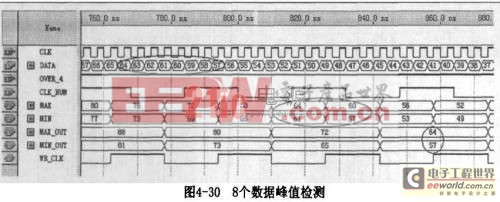

圖4-29和圖4-30是峰值檢測電路時序仿真圖,其中MAX和M取輸出作為觀察峰值檢測模塊內部單次比較結果,MAX_OUT和MIN_OUT是最終比較出的最大值和最小值,WR_CLK可以作為將比較出的數據寫入FPGA內部RAM的寫時鐘信號。圖4-29顯示的是在CLK_NUM周期內只有4個數據進行比較的輸出結果,而圖4-30表示的在CLK_NUM周期內有8個數據進行比較的輸出結果。從兩張圖都可以看到,從數據輸入到數據輸出都有一定的時間延時。雖然數據有延時,但通過這種流水線的方式將模塊的工作速度降了下來,使模塊工作更加穩定,同時也不影響波形的正常顯示。

本峰值檢測模塊在示波器模式和時域測量模式下,經過實驗證明,完全可以捕獲到寬度超過10ns的毛刺信號,而在200MSPS下,可捕獲的毛刺寬度將更窄。

3.3.3時域測量下的觸發

與一般的時域反射儀相比,本設計具有其它產品所沒有的觸發功能,該觸發功能的設計與示波器測量模式下的觸發完好的銜接在一起。脈沖時域測量的觸發不像示波器模式下的觸發那樣,還需要外部觸發模擬電路支持,由于脈沖信號是由數字電路來產生,所以可以直接利用FPGA內部的數字邏輯單元來完成觸發設計,類似于示波器模式下的上升沿觸發,同時為了有效觀察脈沖信號的反射,脈沖信號需要在屏幕上可以左右的移動,在觸發電路設計上也具有預觸發的能力。

預觸發是在數字示波器取代模擬示波器后產生的一種新的觸發方式。這是因為模擬示波器不具備數據存儲的功能,而數字示波器利用它的大量數據存儲能力和軟件處理能力,實現了預觸發功能。有時在某些特定測試情況下,人們感興趣的波形部分并不是緊跟在引起穩定觸發信號的后面,而是在觸發以后一段時間,或者是在觸發之前。這就需要采集系統能夠將觸發事件前后一段時間內發生的信號都存儲下來,以供處理器處理并顯示出來。在實際操作過程中,可

評論