擁有68億個晶體管的大容量FPGA的設計實現

前不久,賽靈思(Xilinx)公司推出了目前業界容量最大的可編程邏輯器件—Virtex-7 2000TFPGA,并開始向客戶供貨。Virtex-7 2000T擁有68億個晶體管,200萬個邏輯單元,相當于2,000萬門ASIC。這也是賽靈思首款采用獨特的堆疊硅片互連(SSI)技術的FPGA。

本文引用地址:http://www.104case.com/article/226807.htm堆疊硅片互連架構解析

賽靈思是第一家采用堆疊硅片互聯(SSI)技術制成商用FPGA的公司,該公司全球高級副總裁亞太區執行總裁湯立人表示,SSI技術的應用成就了賽靈思大容量FPGA,而2.5D IC堆疊技術的率先應用,使得賽靈思能夠為客戶提供兩倍于同類競爭產品的容量并超越摩爾定律的發展速度。

湯立人認為,如果沒有SSI技術,至少要等到下一代工藝技術,才有可能在單個FPGA中實現如此大的晶體管容量。就通常新一代產品的推出而言,SSI 至少提前一年將賽靈思的最大型28nm器件交付給了客戶,這對 ASIC和ASSP仿真和原型而言尤其重要。

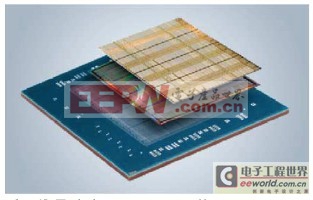

湯立人介紹說,2.5D芯片堆疊技術是指在無源器件上堆疊有源芯片,是主動芯片和被動芯片的堆疊;而3D芯片堆疊技術是指在有源芯片上堆疊有源芯片,是主動芯片和主動芯片的堆疊。賽靈思打造的2.5D堆疊技術是在無源硅中介層上并排幾個硅切片(有源切片),該切片再由穿過中階層的金屬連接,與印制電路板上不同 IC通過金屬互連通信的方式類似。賽靈思是通過將四個不同 FPGA芯片在無源硅中介層上互聯,從而構建了業界目前最大容量的可編程邏輯器件,解決了無缺陷大型單芯片的制造挑戰。

此外, 由于芯片在硅中介層上并排放置,SSI技術能夠避免多個芯片堆疊造成的功耗和可靠性問題。中介層在每個芯片間提供10,000多個高速互連,可支持各種應用所需要的高性能集成。

據了解,SSI技術的真正優勢在于,雖然2000T由4個切片組成,但它仍保持著傳統FPGA的使用模式,設計人員可通過賽靈思工具流程和方法將該器件作為一款極大型FPGA進行編程。這樣設計師可以方便清晰地設計所需要的產品,而且采用這種構架可節約很大一部分空間,設計師可以根據需要再增添所需要的器件。

此次賽靈思推出的Virtex-7 2000TFPGA采用的是2.5D IC堆疊技術,而不是之前提到的3D IC技術,湯立人的解釋是:“賽靈思同樣看好不帶中介層的完全3D IC 堆疊技術前景,但目前3D IC技術面臨著諸多的挑戰,該技術在整個產業中實現標準化還要花更長的時間,3D要真正實現量產還需2年~3年的時間。”

湯立人說,采用SSI技術,讓賽靈思跑在了FPGA廠商的前頭,也使賽靈思讓器件的發展步伐超過了摩爾定律的速度。加速取代ASIC和ASSP

Virtex-7 2000TFPGA除具有68億個晶體管、200萬個邏輯單元外,還包括含有305,400個可配置邏輯塊(CLB),分布式RAM容量高達21,550KB。它共有2160個DSP slice、46,512個BRAM、24個時鐘管理模塊、4個PCIe模塊、36個GTX收發器(每個性能達12.5Gbps)、24個I/O bank和1200個用戶I/O。在降低功耗方面,賽靈思采用的是28nm HPL工藝,靜態時功耗為5W,工作時的功耗僅為19W。

湯立人告訴記者,在28nm工藝技術節點,ASIC或ASSP的NRE超過5000萬美元,而ASIC修改則可能將成本再提升近一半。因此,除非面向最穩定的大批量市場應用,否則ASIC和ASSP的設計只會越來越少被采用。此外,競爭和縮短產品上市時間等這些市場壓力也為定制ASIC的開發帶來了挑戰。在此情況下,用一個Virtex-72000T器件來替代ASIC,就能實現所需要的系統性能和功能。例如,客戶利用賽靈思Virtex-7 2000TFPGA替代大容量ASIC,在總體投入成本相當的情況下,可把開發時間提高2/3(ASIC開發時間長達3年);同時創建集成系統,提高系統帶寬,并因此避免了I/O互連而大幅降低功耗。此外還可以加速先進ASIC系統的原型設計和模擬仿真。

此時,設計人員可以集中精力進行設計,而無需再擔心什么小錯誤會導致災難性的返工修改。此外,Virtex-7 2000T具有可重編程性,如果設計人員犯了錯誤,對器件重新編程就可以了。

目前,SSI技術已成為賽靈思戰略規劃的一部分,未來一年中,賽靈思還計劃通過技術創新,再推出Virtex-7 HTFPGA系列以及SSI 配置。

評論