AT84AD001型ADC在高速信號采集系統中的應用

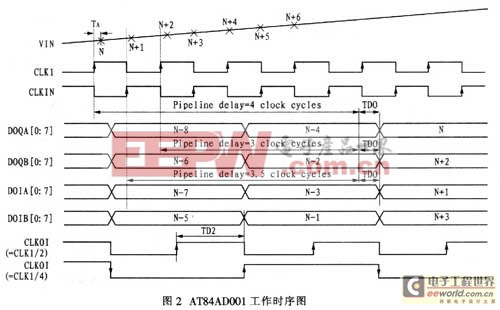

圖2為并行交替工作模式下ADC工作時序圖,兩通道都使用I通道輸入模擬信號,外部輸入時鐘作為I通道工作時鐘,Q通道的工作時鐘與I通道工作時鐘同頻反相,DMUX擇1:2。

在圖2所示的ADC工作時序中,數據輸出延遲TDO是一個固定的延時值,總的延時等于固定延時與流水線傳輸延時之和。在DMUX設置為1:2時,I通道兩組數據的流水線傳輸延時分別為4個時鐘周期和3個時鐘周期,Q通道則分別為3.5個時鐘周期和2.5個時鐘周期,這種設計可以使ADC兩個通道的轉換數據在同一相位輸出,有利于接收系統進行同步數據讀取。5 系統設計

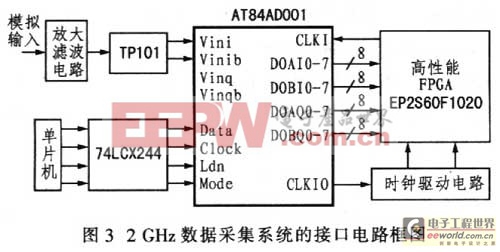

AT84AD001在圖2所示的工作時序下,輸出4路8 bit-500MS/s LVDS邏輯的數據,在采集系統設計中對與其接口器件的性能要求也較高。Altera公司的Stratix2系列FPGA-EP2S60F1020具有高達84個專用LVDS差分邏輯接收通道,每個LVDS通道數據傳輸速率最高達640 MS/s。一片EP2S60F1020即可滿足接收ADC輸出數據和邏輯控制的需要。由于ADC的輸出和FPGA的輸入均設計為LVDS邏輯標準,因此,ADC可直接與FPGA相連。Stratix2系列FPCA內部具有專門的LVDS處理單元,可實現LVDS邏輯的串/并降速轉換,降低速率后的數據可提供給內部DSP處理單元進行處理。Stratix2系列FPGA的另外一個優點是其內部具有專門的高速數字鎖相環電路,能夠產生可供ADC電路使用的時鐘信號。

圖3所示為基于AT84AD001的2GHz數據采集系統的接口電路框圖。模擬輸入信號經過前置放大濾波電路,再經過一個射頻變壓器TP101將單端信號轉換為差分信號,送入AT84AD001的I通道模擬輸入端,由于所選的特殊的工作方式,Q通道的模擬輸入端無須輸入信號。ADC的工作時鐘CLKI由FPGA提供,FPGA輸入一個頻率較低的時鐘,經內部數字PLL倍頻和邏輯組合產生頻率為1GHz的工作時鐘,作為ADC的采樣時鐘CLKI。在圖2所示的工作模式下,ADC的數據準備信號CLKIO可以作為系統數據采集和處理的同步時鐘,CLKIO為差分LVDS邏輯,速率為250MS/s,在時鐘的上升沿和下降沿均起作用。ADC輸出4路8bit-500MS/s的數據,共占用FPGA的32個LVDS邏輯輸入通道。ADC的三線串行接口通過一個AVR系列單片機ATmegal28L進行控制,其中單片機產生的信號邏輯電壓為3.3V,而ADC三線接口邏輯電壓為2.25V,因此需要在單片機和ADC之間加一個緩沖器74LCX244進行電平轉換。

6 結束語

介紹了采用高速BiCMOS技術的AT84AD001型模數轉換器,并將其應用在2 GHz數字采集系統中。它的典型三線串口功能簡化了ADC的外圍電路設計,提高了超高速電路的性能。由AT84AD001及其接口器件EP2S60F1020構成的數據采集系統采樣速率達到了2GS/s,可以應用在現代寬帶通信中。隨著現代超寬帶技術的發展,這種超高速數據采集方案可以用來設計一種全數字化超寬帶(UWB)接收器的數據采集系統,以便將軟件無線電技術應用于超寬帶通信系統中,而高速ADC在全數字化超寬帶接收器的設計中起了關鍵作用。

評論