基于FPGA的IPV6數(shù)字包的拆裝實(shí)現(xiàn)

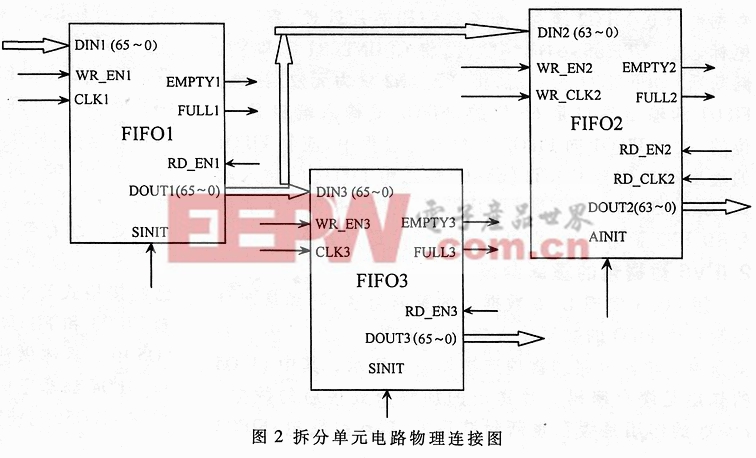

圖中的三個(gè)FIFO都是由Xilinx公司的開發(fā)工具ISE6.1自帶的Core IP生成的。其中FIFO1和FIFO3是同步FIFO,工作時(shí)鐘為頻率62.5MHz,輸入輸出數(shù)據(jù)寬度都是66bit;FIFO2是異步FIFO,輸入時(shí)鐘頻率為62.5MHz,輸出時(shí)鐘頻率為50MHz(密碼芯片的工作時(shí)鐘頻率為50MHz),輸入輸出數(shù)據(jù)寬度都是64bit。

FIFO1的輸入數(shù)據(jù)為IPV6數(shù)據(jù)包。可以看出,該數(shù)據(jù)是以并行的66bit信號(hào)傳輸?shù)模疵恳粫r(shí)鐘周期并行傳送66bit數(shù)據(jù),其中每個(gè)周期的高兩位(即65位和64位)為數(shù)據(jù)包的頭尾標(biāo)志,這是IPV6路由器內(nèi)部根據(jù)實(shí)際處理需要加上的,“10”表示一個(gè)完整數(shù)據(jù)包的第一周期,“11”表示數(shù)據(jù)包的中間內(nèi)容,“01”表示一個(gè)完整數(shù)據(jù)包的最后一個(gè)周期。因?yàn)?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/IPV6">IPV6數(shù)據(jù)包的包頭是固定長(zhǎng)度的,為40字節(jié)(等于5×64bit),故數(shù)據(jù)的前五個(gè)周期為IPV6數(shù)據(jù)包的包頭,包頭后面跟的就是數(shù)據(jù)包的數(shù)據(jù)部分。

下面討論IPV6數(shù)據(jù)包的包頭和數(shù)據(jù)部分的拆分過(guò)程。

首先判斷FIFO1輸入端數(shù)據(jù)的頭尾標(biāo)志DATA(65~64)與FIFO1的滿標(biāo)志FULL1,如果DATA(65~64)=“10”且FULL1=“0”,即判斷到一個(gè)完整數(shù)據(jù)包的開始且FIFO1未滿,則使FIFO1的寫使能WR_EN1有效,寫入數(shù)據(jù);如果DATA(65~64)=“01”,好判斷到一個(gè)完整數(shù)據(jù)包結(jié)束時(shí),則使WR_EN1無(wú)效,這樣一個(gè)完整的數(shù)據(jù)包就緩存到了FIFO1時(shí)。

當(dāng)判斷到FIFO1的空標(biāo)示EMPTY1=“0”,即FIFO1非空間,令FIFO1的讀使能信號(hào)RD_EN1有效,將FIFO1中的數(shù)據(jù)讀出,直到EMPTY1=“1”,即FIFO1空為止。對(duì)讀出的數(shù)據(jù)設(shè)定一計(jì)數(shù)器COUNTER1進(jìn)行計(jì)數(shù),當(dāng)DONT1不為0即FIFO1輸出端有信號(hào)時(shí)開始計(jì)數(shù)。當(dāng)0COUNTER1=5時(shí),令FIFO3的寫使能信號(hào)WR_EN3有效,將數(shù)據(jù)包的包頭寫FIFO3緩存;當(dāng)COUNTER1>5時(shí),令WR_EN3無(wú)效,WR_EN2有效,將IPV6數(shù)據(jù)包的數(shù)據(jù)部分送FIFO2緩存,準(zhǔn)備送密碼芯片處理,直到頭尾標(biāo)志DOUT1(65~64)=“01”時(shí),將COUNTER1清零,在判斷到COUNTER1為0后,將WR_EN2置為無(wú)效。注意:FIFO1的輸出端口是66位,F(xiàn)IFO2的輸入端口是64位的,故在FIFO1向FIFO2寫數(shù)據(jù)的過(guò)程中,應(yīng)將FIFO1的輸出端口信號(hào)DOUT(63~0)傳送給FIFO2的輸入端口DIN2(63~-)。當(dāng)判斷到FIFO2非空間,將其讀使能信號(hào)RD_EN2置為有效,即可向密碼芯片送出數(shù)據(jù)。

相關(guān)推薦

-

-

-

-

sandman555 | 2005-02-05

-

-

herbertwj | 2004-08-15

-

-

-

-

sandman555 | 2005-02-05

-

sandman555 | 2005-02-05

技術(shù)專區(qū)

- FPGA

- DSP

- MCU

- 示波器

- 步進(jìn)電機(jī)

- Zigbee

- LabVIEW

- Arduino

- RFID

- NFC

- STM32

- Protel

- GPS

- MSP430

- Multisim

- 濾波器

- CAN總線

- 開關(guān)電源

- 單片機(jī)

- PCB

- USB

- ARM

- CPLD

- 連接器

- MEMS

- CMOS

- MIPS

- EMC

- EDA

- ROM

- 陀螺儀

- VHDL

- 比較器

- Verilog

- 穩(wěn)壓電源

- RAM

- AVR

- 傳感器

- 可控硅

- IGBT

- 嵌入式開發(fā)

- 逆變器

- Quartus

- RS-232

- Cyclone

- 電位器

- 電機(jī)控制

- 藍(lán)牙

- PLC

- PWM

- 汽車電子

- 轉(zhuǎn)換器

- 電源管理

- 信號(hào)放大器

評(píng)論