利用低成本FPGA設計下一代游戲控制臺

高速的芯片至芯片互連

FPGA通過高速的芯片至芯片互連技術與GPU和CPU連接,這些技術包括HyperTransport、PCI Express或串行RapidIO。串行RapidIO和PCI Express是串行而非并行技術,即串行地發送數據,并通過LVDS以數據包的形式恢復數據,而不是一次恢復一位。從并行到串行接口的轉換系統可用較少的線路達到同樣的高速數據速率。

源同步和時鐘數據恢復接口

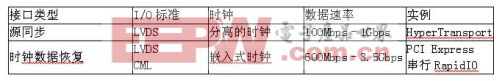

HyperTransport是一個源同步接口,而PCI Express和串行RapidIO采用時鐘數據恢復(CDR)技術,如下表所示。對于源同步接口而言,傳送方提供數據和差分時鐘,這樣就能較容易地在高達700Mbps的數據速率捕獲數據。

源同步和時鐘數據恢復接口。

當數據速率超過700Mbps時,數據通道之間的偏移成為數據有效窗的重要部分,特別是對寬數據通道而言。有些FPGA具有自動對齊功能,能夠針對源同步接口管理數據偏移,從而有助于它們達到超過800Mbps的LVDS數據速率(有些情況下高達2Gbps)。

對于CDR接口而言,并沒有提供額外的差分時鐘。取而代之的是時鐘包含在串行數據包中,必須從數據中恢復出來。因此,對于CDR來說時鐘偏移不是一個問題,這與源同步不同。利用SERDES高速串行地發送數據包,CDR接收器將對數據本身鎖定相位以取得時鐘。

對于CDR而言,在高速情況下,SERDES抖動是主要問題。抖動是指期待數據傳輸的位置發生了變化,使得難以準確地接收到數據包。如圖3所示的眼圖,抖動使得圍繞眼睛的黃色帶的寬度發生變化,圖中用紅色表示。

圖3:CDR眼圖。

有些抖動是隨機的,但大部分抖動是確定性的,是由于其它信號以及靠近數據信號的半導體元件的開關操作引起,或者是由數據模式的特性、傳輸的不平衡上升及下降時間所引起。

評論