最佳FPGA和專用DSP

DSP選擇

做為這些通用功能應用,大多數DSP應用的核心是乘、加、減或累加。通用DSP芯片與通用微處理器結合能有效地實現這些功能。乘法器數量通常1~4個,而微處理器通過乘和其他功能定序通過的數據,存儲中間結果在存儲器或累加器。主要靠提高乘法所用的時鐘速度來提高性能。典型時鐘速度為幾十MHz~1GHz。性能用每秒MMAC(百萬乘累加)度量,典型值10~4000。

需要較佳功能必須并聯組合多個DSP引擎。這種方法的主要優點是直接實現用高級編程語言(如C語言)編寫的算法。

DSP定向的FPGA能在一個芯片上并行實現很多功能。通用發送、邏輯和存儲器資源互連功能、執行加法功能、定序和存儲數據。某些基本器件僅提供乘法支持,需要用戶建造其他邏輯功能。更復雜的器件提供加、減和累加功能做為DSP構建單元的一部分。FPGA通常帶有幾十乘法器單元,可工作在幾百MHz的時鐘頻率。

DSP FPGA選擇

Altera公司的Cyclone FPGA不包含DSP定向的元件,這使得實現大的DSP功能而不消耗大量的外部資源變得困難。然而,CycloneII包含乘法器功能,Xilinx公司的SpartanIII FPA家族具有基本的乘法器功能。沒有DSP功能時,必須消耗大量的FPGA資源來實現一般設計中的加、減、累加和流水線寄存器。

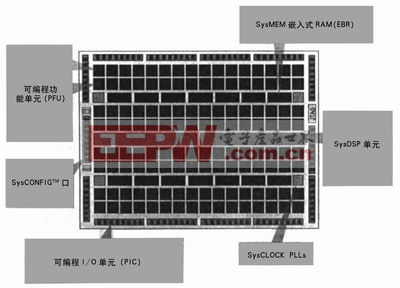

Lattice公司專為DSP應用設計了ECP-DSP器件(圖4)。它含有與4和10個集成sysDSP單元連接的低成本FPEA結構。sysDSP單元以3個數據通路寬度(9,18和36)支持4個功能單元。用戶為DSP單元選擇一個功能單元,然后選擇其操作數的寬度和類型(符號/無符號)。sysDSP單元中的操作數可以帶符號或無符號,但在功能單元中不能混合。

同樣,在一個單元中操作數寬度不能混合。每個sysDSPK中的資源可配置來支持MULT(乘)、MAC(乘累加)、MULTADD(乘加/減)和MULTADDSUM(乘加/減和)元件。

圖4 ECP-DSP框圖

每個單元中可用的元件數取決于所選擇的數據通路寬度。把若干個元件連接起來可并聯實現DSP功能。

sysDSP單元在輸入,中間和輸出級具有內置任選流水線寄存器。如需要,輸入也可能并行輸入或跨過陣列移位。也為帶符號和不帶符號運算和加減之間動態轉換提供選擇。在sysDSP單元中可得到流水線寄存器、和、減和累加。在一般的功能中,一般需要用加、和或累加組合乘法。概念簡單的流水線寄存器在寬數據通路中實現要消耗大量的資源。用sysDSP單元實現這些功能可使通用FPGA資源消耗較低、性能較高,允許采用較低速度等級的更小器件。

評論