基于FPGA的微型數字存儲系統設計方案

按照上述控制邏輯關系編寫CY7C68013的同件程序。CY7C68013有3種可用接口模式:端口、GPIF主控和從FI-FO。“GPIF主控”接口模式使用PORTB和PORTD構成通向4個FX2端點FIFO(EP2、EP4、EP6和EP8)的16位數據接口。GPIF作為內部的主控制器與 FIFO直接相連.具有6個可編程控制輸出信號(CTR0~CTR5)和6個通用準備就緒輸入信號(RDY0~RDY5),用戶可通過編程設置控制信號的輸出狀態,即器件在接收到何種就緒信號后執行相應操作,GPIF控制代碼存放于器件內部RAM的波形描述器中。從該系統需求出發,將CY7C68013設為FIFO Read模式,使GPIF中的Slave FIFO與USB通信中端點緩沖直接建立連接,數據傳送無需CPU參與。

固件程序代碼設計主要是根據系統需求設計相應的程序框架圖,再調用同件函數庫 (Ezusb.lib)的函數進行編程,初始化并重新列舉端點,然后在任務處理器中設定任務,在Keil C51環境中編譯代碼。編譯通過后,將同件代碼下載到USB單片機中,即可實現GPIF多字節讀操作。

4 系統可靠性驗證

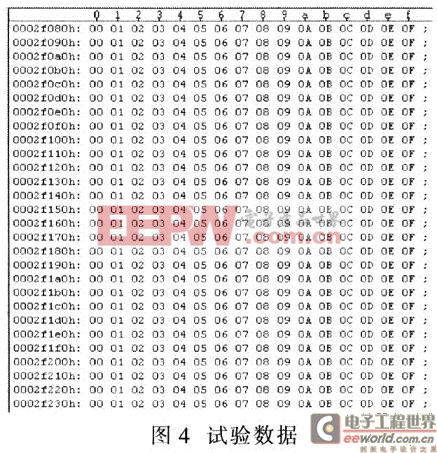

為驗證系統可靠性,在數據輸入端循環輸入00~0F遞增數據,通過上位機讀出、寫入Flash中的數據,圖4為試驗數據。通過讀出的數據驗證了該系統數據存儲及回讀的正確性、可靠性。

5 結束語

采用FPGA對Flash進行讀、寫、擦除操作,利用狀態機分時控制3種操作,簡化程序設計,簡單修改地址將Flash的容量從32 MB增加到1 GB,提高了系統的可移植性、可擴展性和通用性,便于維護設備,有利于產品的優化和改進,縮短了開發周期。采用USB單片機與PC機建立通信連接,與現有設備很好兼容,數據讀取速度可達1O MB/s,可方便、快捷地讀取數據。通過多次驗證,該系統工作穩定、可靠。

評論