基于FPGA的PCB測試機硬件電路設計研究

由于這兩種器件都是SPI接口,可將這兩器件連接至同一SPI 總線,通過不同的片選信號對不同的器件操作。 由于SPI接口協議復雜,而且從圖3 可以看出,這兩種器件的時序并沒有用到全部的SPI接口時序。為了實現符合以上邏輯的時序,減少標準SPI 接口IP 核對FPGA資源的浪費, 設計采用Verilog硬件描述語言用同步狀態機(FSM)的設計方法實現,編寫

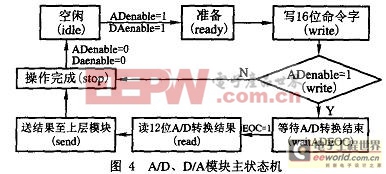

系統設計中,將AD、DA操作封裝成一單獨模塊,由上層控制模塊輸出命令字及控制信號啟動本模塊的相應操作,操作完成后(進入idle狀態) ,本模塊發出相應狀態信號至上層模塊。

FPGA 程序框架

FPGA 片內程序是整個測試系統正確運行的關鍵。 由自頂向下的FPGA 設計原則,將系統分為5個獨立的模塊, 即通信模塊(ISA) 、測試模塊(TEST) 、AD/DA 模塊、解碼模塊(DECODER) 、RAM 控制模塊(RAMCTL)。

ISA 模塊:系統通信及控制模塊,完成與上位機通信、命令字解釋、控制信號的產生等。系統根據上位機傳送的導通電阻、絕緣電壓等參數啟動ADDA模塊完成參考電壓的輸出;根據測試命令啟動測試模塊完成測試過程。數據在多個同步運行的同步狀態機間傳送,較難控制的是多進程間的數據通信與數據同步。

RAM控制模塊:在測試開始前,上位機將測試點的信息通過總線傳送至ISA模塊, ISA 模塊再將其存放到片內RAM中;測試完成后,將RAM中的測試結果傳送到上位機。 在測試時測試模塊通過讀RAM中測試點的信息來打開相應測試開關,再將測試結果保存到RAM 中。 這樣兩個模塊都要求讀寫RAM 以實現兩個模塊之間的數據共享,這就要求有一控制信號將兩組讀寫信號線分別與RAM模塊相連接,RAM控制模塊即完成此功能。測試模塊(TEST):雖然測試過程有多種,如開關卡自檢、導通測試、絕緣測試等,但測試過程卻是相同的,即測試掃描。 測試的工作過程是:加比較電路參考電壓→打開待測點開關→延時→讀比較器結果→測試另一組測試點。 本模塊是按照不同的操作碼,進入不同的測試過程。 測試結果與測試點編號一起組成13 位數據保存到RAM 中,并將原來測試點的編號信息覆蓋。

解碼模塊(DECODER):這一模塊掛在測試模塊(TEST) 之后,它完成開關編號到實際電路的映射。 由于測試針陣形式不同、譯碼電路與控制電路的硬件設計不同,上級模塊輸出的測試開關信息并不能直接作為輸出控制測試開關電路。 解碼模塊完成這兩者間的轉換。

AD/DA 模塊(AD/DA):設計SPI 總線接口對A/D 及D/A 器件操作,模塊以允許(adenable , daenable) 信號啟動,以busy信號作為轉換完成標志信號,將A/D及D/A操作相對其它模塊進行封裝。系統的每個模塊采用Verilog硬件描述語言編寫,采用多個多層嵌套的同步狀態機(FSM)完成整個系統的邏輯功能;每一模塊應用仿真工具Modelsim完成模塊的功能仿真,系統完成功能測試后;利用Altera 綜合布線工具QuartusII完成系統后仿真及綜合、布線、下載;充分利用Altera公司免費提供的IPcore 對程序模塊進行優化;頂層設計采用方框圖輸入方式,模塊間的數據流由方框圖更直觀地表現出來。

結束語

基于FPGA的PCB測試機的硬件控制系統,提高了PCB測試機的測試速度、簡化電路的設計。此外由于FPGA的可重構特性,為系統的軟件算法以及硬件結構的進一步優化升級打下了良好的基礎,具有良好的應用前景。

評論