基于MPC8260處理器和FPGA的DMA接口設計

BD(Buffer Descriptors)表是用于指定傳輸方式、源/目的地址和數據長度等基本信息的數據結構。BD表的基地址由參數RAM中IBASE寄存器的值指定。除IDMA BD表的基地址之外,IDMA參數RAM內還存放有IDMA BD指針、IDMA傳輸緩沖區的起始地址、IDMA傳輸緩沖區大小和DMA通道模式等IDMA通道信息。IDMA參數RAM的基地址由參數RAM中IDMAx_BASE寄存器的值指定。IDMAx_BASE寄存器的地址是固定的,如IDMA1_BASE在偏移RAM基地址0x87FE的位置。CP就是通過IDMAx_BASE寄存器找到IDMA參數RAM,再通過IBASE找到BD表的順序初始化IDMA通道的。具體的寄存器配置可以參考文獻[1]第19章的IDMA編程示例。

為了提高通道的傳輸速率,系統中IDMA通道初始化應該注意以下幾點:

① 需要在SIU中為FPGA配置UPM模式控制MPC8260和FPGA之間的突發讀寫。不要使用通用目的片選機(GeneralPurpose Chipselect Machine,GPCM)模式。因為MPC8260內存控制的GPCM模式不支持突發傳輸,IDMA工作在GPCM模式下一方不論傳輸數據的長度是否滿足突發的要求,都只能以普通的單次讀寫進行。

② 把FPGA當作存儲器操作,IDMA工作在內存到內存的雙地址模式下,緩沖區設為最大的2 KB。

③ BD表的配置應該與FPGA中的緩沖區一一對應。BD表結構中的CM(Continuous Mode)位應該設置為緩沖鏈模式,在每一個BD表傳輸完之后,清BD表的有效位;同時,CP根據下一個BD表的值自動裝載IDMA寄存器進行后面的傳輸。

IDMA通道初始化以后等待CP發出START_IDMA命令開始傳輸。在最后一個BD表傳輸結束時觸發中斷信號通知PowerPC內核本次傳輸過程的完成。傳輸過程中會發生改變的通道設置寄存器包括IDMA BD表指針、源地址、目的地址和BD表有效位等,所以在BD表傳輸結束的中斷處理程序中需要恢復這些寄存器為下一次傳輸作準備。

2.1.2 中斷處理

系統設計中使用了兩類中斷方式: IRQ引腳引入的外部中斷和CPM觸發的內部中斷。初始化過程包括:使能對應的中斷屏蔽位、選擇中斷優先級、連接對應中斷向量號和中斷服務程序等。為了保證較好的傳輸實時性,需要把中斷優先級盡量設得高一些。

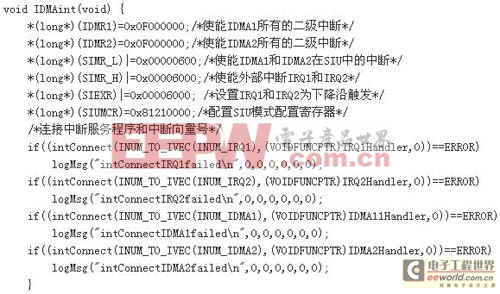

與一般中斷處理過程的區別在于:MPC8260中斷處理控制器采用分級結構來擴展中斷信號總數。CPM內的中斷就是二級中斷,需要通過CPM中斷控制器和SIU中斷控制器兩級中斷控制。本設計中用來通知內核本次傳輸過程結束的中斷是CPM內最后一個BD表傳送結束的信號BC(BD Completed)。BC信號和命令結束等幾個信號一起通過SIU中斷掛起寄存器中的IDMA位向內核發出中斷信號。所以在中斷初始化時要同時有效IDMA屏蔽寄存器和SIU中斷屏蔽寄存器對應的比特位。具體的中斷初始化實例如下:

尤其要注意的是,中斷處理程序結束之前的清SIU中斷掛起寄存器,不能直接在SIU中斷掛起寄存器的IDMA位寫1,而是要通過在IDMA事件寄存器的BC位寫1來間接地清SIU中斷掛起寄存器。

2.2 FPGA部分程序

系統中的FPGA芯片選用Xilinx公司的VirtexII 3000。利用VirtexII內嵌的大容量BlockRAM配置為單口RAM來做緩沖區,在程序中可以用Xilinx的集成開發環境ISE 7.1i內部自帶的IP核生成。對FPGA來說,由于數據的輸入/輸出都是順序的,所以兩端都只要1根地址線用于區分相鄰的兩個數據就可以了。地址線配合內部計數器構成讀寫指針,當寫指針從緩沖區的一半跳到另外一半時發相應的中斷信號。

FPGA設計的關鍵部分是和MPC8260的總線接口設計。通過適當選擇緩沖區的起始地址和長度,可以使MPC8260讀FPGA都以突發的方式進行。設計中,MPC8260對FPGA的突發讀寫遵循自己配置的UPM模式,所以要綜合考慮UPM模式設計和FPGA讀寫邏輯設計。在設計UPM模式時,可以在每次MPC8260鎖定數據總線數據之前由通用功能信號線(General Purpose Line,GPL)產生一個下降沿通知FPGA往數據總線上寫新數據;或者通過GPL把總線時鐘送到FPGA達到收發同步來完成MPC8260與FPGA之間的讀寫。

3 總結

結合MPC8260的中斷處理和IDMA傳輸機制,設計了一種MPC8260和FPGA之間的高速數據傳輸接口。測試結果顯示:采用循環讀的方式把FPGA中的數據復制到SDRAM中,數據傳輸速率只有11 Mbps左右;而采用本文介紹的IDMA方式,最高速率能夠達到500 Mbps,并且內核占用率較低,實驗結果完全能夠滿足系統設計需求。本研究對于

參考文獻

[1] Freescale. MPC8260 PowerQUICCTM II Family Reference Manual .MPC8260RM Rev.2, 2005-12.

[2] Freescale. MPC8260 PowerQUICCTM II IDMA Functionality.Rev. 3,2006-02.

[3] Freescale. MPC8260 IDMA Timing Diagrams. Rev. 4,2006-07.

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論