基于FPGA的數(shù)據(jù)采集控制模塊的研究與設計

2.2 A/D轉(zhuǎn)換控制器的設計

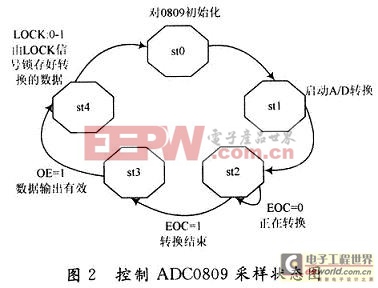

在此設計中,是利用狀態(tài)機對A/D轉(zhuǎn)換進行控制的。控制ADC0809采樣狀態(tài)圖,如圖2所示。

在狀態(tài)ST0中,對0809進行初始化,之后進入到狀態(tài)ST1;在狀態(tài)ST1中,ALE和START信號有效,這時EOC信號變?yōu)榈碗娖剑M入轉(zhuǎn)換狀態(tài)ST2。此時,需要對0809工作狀態(tài)信號EOC進行測試,如果為低電平,表示轉(zhuǎn)換沒結(jié)束,仍需要停留在ST2狀態(tài)中等待,直到變成高電平后才說明轉(zhuǎn)換結(jié)束,在下一時鐘脈沖到來時轉(zhuǎn)向狀態(tài)ST3。在狀態(tài)ST3,由狀態(tài)機向0809發(fā)出轉(zhuǎn)換好的8位數(shù)據(jù)輸出允許命令,這一狀態(tài)周期同時可作為數(shù)據(jù)輸出穩(wěn)定周期,以便能在下一狀態(tài)中向鎖存器中鎖入可靠的數(shù)據(jù)。在狀態(tài)ST4,由狀態(tài)機向FPGA中的鎖存器發(fā)出鎖存信號,將0809輸出的數(shù)據(jù)進行鎖存。

2.3 RAM讀寫控制器的設計

在該模塊設計中,RAM讀寫控制模塊又分為讀控制模塊、寫控制模塊和讀寫狀態(tài)轉(zhuǎn)換模塊。寫控制模塊中兩個輸入信號分別與A/D轉(zhuǎn)換控制模塊的數(shù)據(jù)鎖存和轉(zhuǎn)換輸出相連。當鎖存信號使能,即發(fā)出寫信號,將數(shù)據(jù)存儲到外部RAM的第600個地址空間之后,再對之前的數(shù)據(jù)進行前移,以達到數(shù)據(jù)的及時更新。讀控制模塊的控制信號分別與寫更新完畢信號和讀信號相連,當寫更新完畢信號使能時,只要接到讀信號,則依次讀完外部RAM前600個地址空間(一場)的數(shù)據(jù)。

2.4 鍵盤掃描控制器的設計

鍵盤控制模塊由四個模塊組成,包括:時鐘分頻模塊、行鍵值輸出模塊、鍵值鎖存模塊和鍵值合成模塊。鍵值鎖存模塊將按下按鍵的行、列信息鎖存,并交由鍵值合成模塊,該模塊配合行鍵輸出模塊輸出的結(jié)果進行查表,最終確定鍵值。

3 仿真結(jié)果

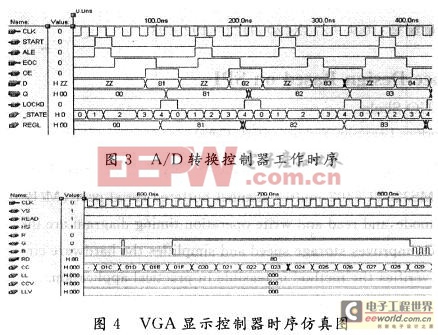

Max+PlusⅡ仿真平臺的圖形輸入方式直觀,符合傳統(tǒng)數(shù)字系統(tǒng)設計人員的習慣,便于進行接口的設計,容易實現(xiàn)仿真,便于信號的觀察。基于以上考慮,利用此平臺,用硬件描述語言VHDL來實現(xiàn)各個功能模塊,A/D轉(zhuǎn)換控制器和VGA顯示控制器模塊的時序仿真結(jié)果如圖3、圖4所示。

4 結(jié) 語

這里的數(shù)據(jù)采集控制模塊主要以FPGA為基礎,本著軟件硬件化的思路,著重研究主控制模塊的實現(xiàn)。由于采用FPGA作為控制處理器,其速度快,效率高,且標準的VGA接口使得系統(tǒng)的使用更加便捷,鍵盤控制的多通道間切換,也為實現(xiàn)多路采集奠定了基礎。

評論