高速流水線浮點加法器的FPGA實現

圖3所示是其仿真的波形圖。

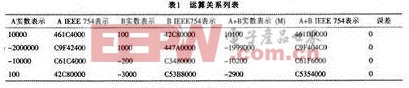

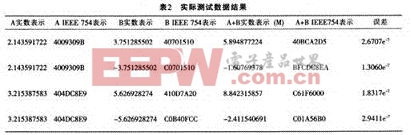

從圖3可以看出表1所列的各種運算關系。表2所列為其實際的測試數據。

表中“A+B實數表示(M)”指Matlab計算的結果;“誤差”指浮點處理器計算結果與Matlab計算結果之差。

綜上所述,本工程設計的浮點加法器所得到的運算結果與Matlab結果的誤差在10-7左右,可見其精度完全能夠符合要求。

5 結束語

本工程設計完全符合IP核設計的規范流程,而且完成了Verilog HDL建模、功能仿真、綜合、時序仿真等IP核設計的整個過程,電路功能正確。實際上,本系統在布局布線后,其系統的最高時鐘頻率可達80MHz。雖然使用浮點數會導致舍入誤差,但這種誤差很小,可以忽略。實踐證明,本工程利用流水線結構,方便地實現了高速、連續、大數據量浮點數的加法運算,而且設計結構合理,性能優異,可以應用在高速信號處理系統中。

評論