基于FPGA和DDS的信號(hào)源研究與設(shè)計(jì)

4.2 基于1/4波形的存儲(chǔ)器設(shè)計(jì)

為了提高系統(tǒng)的分辨率和降低FPGA資源的利用率,采用基于1/4波形的存儲(chǔ)器設(shè)計(jì)技術(shù)。利用正弦波對(duì)稱性特點(diǎn),只要存儲(chǔ)[O~π/2]幅值,通過(guò)地址和幅值數(shù)據(jù)變換,即可得到整個(gè)周期內(nèi)的正弦波,其設(shè)計(jì)原理如圖2所示。

用相位累加器輸出高2位,作為波形區(qū)間標(biāo)志位。當(dāng)最高位與次高位都為“0”時(shí),表示輸出正弦波正處在[0~π/2]區(qū)間內(nèi),這時(shí),地址與輸出數(shù)據(jù)都不需要變換;當(dāng)最高位為“0”,次高位為“l(fā)”時(shí),輸出正弦波正處在[π/2~π]區(qū)間內(nèi),這時(shí),地址變換器對(duì)地址進(jìn)行求補(bǔ)操作,而輸出數(shù)據(jù)不變;當(dāng)最高位為“l(fā)”,次高位為“0”時(shí),輸出正弦波正處在[π~3π/2]區(qū)間內(nèi),這時(shí),地址不變,而輸出變換器對(duì)輸出數(shù)據(jù)進(jìn)行求補(bǔ)操作;當(dāng)最高位與次高位都為“l(fā)”時(shí),輸出正弦波正處在[3π/2~2π]區(qū)間內(nèi),這時(shí),地址和輸出數(shù)據(jù)都進(jìn)行求補(bǔ)操作。

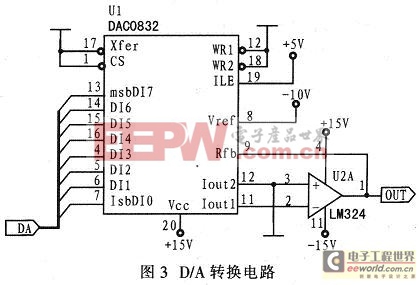

5 D/A轉(zhuǎn)換電路

數(shù)據(jù)

為降低設(shè)計(jì)成本,采用8位廉價(jià)

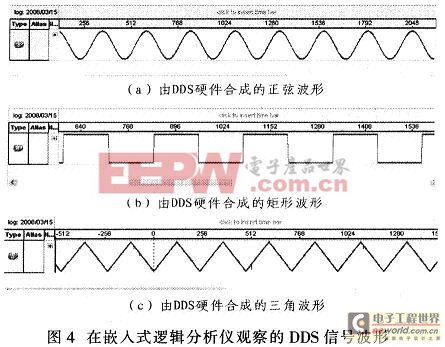

6 驗(yàn)證結(jié)果

為驗(yàn)證本系統(tǒng)的設(shè)計(jì)正確性,利用Ouarlus II軟件的

7 結(jié)論

直接數(shù)字頻率合成(DDS)技術(shù)屬第三代頻率合成技術(shù),與第二代基于鎖相環(huán)頻率合成技術(shù)相比,利用DDS技術(shù)合成的輸出波形具有良好的性能指標(biāo)。本文在DDS技術(shù)工作原理的基礎(chǔ)上,介紹基于FPGA實(shí)現(xiàn)DDS的設(shè)計(jì)方法,并給出該系統(tǒng)合成的波形,從測(cè)試結(jié)果可看出,該系統(tǒng)工作穩(wěn)定、可靠,并具有較好的參考與實(shí)用價(jià)值。

評(píng)論