基于FPGA的PXA270外設時序轉換接口設計

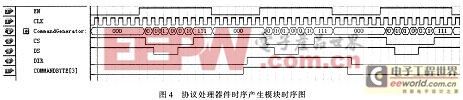

圖3為COM20020的時序原理圖,從時序分析可得出如下設計方案:DIR用于指示操作是讀還是寫,DIR=‘1’為讀,否則為寫。在操作前先對DIR 賦值;在EN有效時選擇CS,CLK的下一次上升沿變為有效。這樣是給寫操作對COM20020數據總線準備數據之用,不影響讀操作;DS選擇在CS有效的下一個CLK上升沿變為有效,但在CS無效前兩個時鐘周期給出上升沿,以滿足“片選信號CS必須先于DS至少5 ns,并且只能在DS無效之后恢復為高電平”,并且DS中間應有至少60ns的時鐘寬度,因而保持3個CLK周期有效。圖4為CommandGenerator時序仿真圖。采用計數器進行時序同步。以下給出VHDL源代碼。

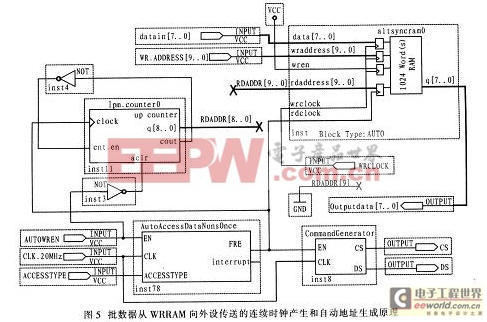

圖5為批數據從WRRAM向外設傳送的連續時鐘產生和自動地址生成原理圖。其中,lpm_counter0為帶有異步清零和進位信號的增計數; AutoAccessDataNumsOnce在EN='1'時,產生一次批傳送時鐘,根據COM20020的長短數據包傳送要求,在CCESSTYPE =‘1’時傳送長數據包(512 B),否則傳送短數據包(256 B)。FRE信號同時提供WRRAM的rdclock和lpm_counter0的clock信號。

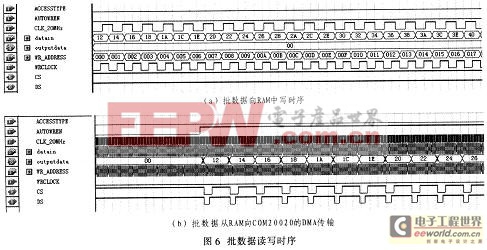

圖6為一次批數據向RAM中寫,而后啟動DMA傳輸,將數據從RAM送至COM20020的時序仿真。在WRCLOCK上升沿時,RAM將datain總線上的數據存儲到WR_AD-DRESS所指向的字節地址空間,WRCLOCK信號是由PXA270的WE信號與分配給RAM的片選信號(高電平有效)相與而得。對RAM進行

3.3 對外設指定寄存器操作

對外設指定寄存器操作比批數據傳送實現簡單,只需將操作次數降為1次,并對 COM20020的A2~A0提供相應的地址即可。指定寄存器操作將數據存儲在RAM的高512字節空間,并且只占用其中低8個字節,在PXA270編程時,需確保PXA270送入RAM的地址與命令寄存器中的RAM存儲地址COMMANDBYTE[2..0]相對應。

4 結論

本設計解決ARCNET協議專用器件應用于列車通信網絡中的時序匹配問題,實現了PXA270處理器與COM20020的時序轉換。此外,對擴展其他總線訪問類型提供了參考框架,可通過修改CommandGenerator中COM20020時序,實現不同外設總線訪問類型的擴展;修改 AutoAccessDataNun-sOnce中的ACCESSTYPE,可配置批數據操作的數據種類。

評論