基于FPGA的高速串行交換模塊實現方法研究

4 交換模塊實現的關鍵技術

在此交換模塊中,關鍵技術集中在PCIE的DMA實現上,本節將討論存儲器寫模式下的TLP結構以及基于FPGA實現的PCIE的DMA寫操作核心狀態機的設計與實現。

4.1 TLP結構簡介

PCIE設備之間以數據包形式傳送信息,最主要類型的數據包是處理層數據包TLP。其包格式如圖5。

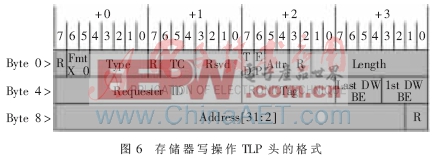

事務是在PCIE請求者和完成者之間進行的操作,包括存儲器事務、IO事務、配置事務和消息事務。本文討論的DMA讀寫操作是針對存儲器空間的操作,存儲器寫操作TLP頭的格式如圖6。

4.2 PCIE的DMA寫操作的設計與實現

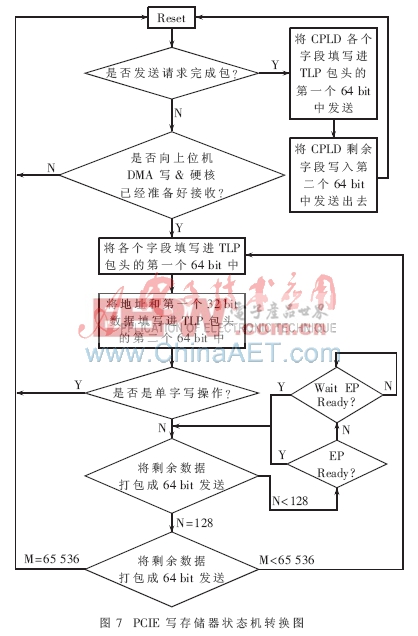

PCIE的DMA寫操作實現的主要方法是將TLP包頭中的各個字段正確填充,并將數據按照64 bit或者32 bit并行放在TLP包頭后,按照64 bit或者32 bit并行傳輸給PCIE硬核,由硬核以PCIE協議串行傳輸給其他設備。PCIE的寫操作封裝在TX模塊的狀態機中。在本設計中規定一次DMA寫操作分為65 536次包傳輸,每次包傳輸的最大載荷為128 B,一次寫操作的傳輸數據為8 MB。其狀態機轉換模型如圖7(CPLD指返回完成包)。

實際上FPGA在PCIE硬核中實現了8個TLP存儲空間,因此當發送模塊將8個以上的TLP包傳輸給硬核后,硬核可能會堵塞,因此發送模塊與硬核之間的交互非常必要。

評論