在Virtex-5 FPGA芯片中使用CRC硬模塊

CRC模塊

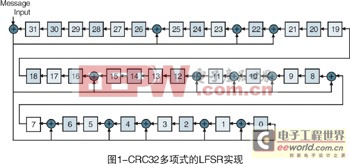

CRC 的硬件實現(xiàn)使用一個簡單的 LFSR。這種電路雖然實現(xiàn)起來簡單,但對于一個n位數(shù)據(jù)流來說,要占用n個時鐘周期來計算CRC值。在必須以較高速度處理數(shù)據(jù)幀的高速數(shù)據(jù)網(wǎng)絡(luò)應(yīng)用中,這樣的延遲是無法忍受的。這類高速網(wǎng)絡(luò)應(yīng)用迫切需要對并行數(shù)據(jù)流實現(xiàn)CRC生成和校驗。

Virtex-5 LXT/SXT器件中實現(xiàn)的CRC模塊可幫助設(shè)計人員加速校驗和計算。

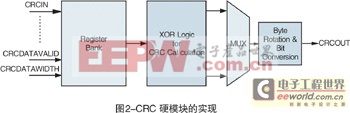

Virtex-5 LXT/SXT器件中的 CRC硬模塊基于CRC32多項式。Virtex-5 FPGA含有CRC32和 CRC64 兩種硬模塊,能以一個時鐘周期的延遲為4位和8位數(shù)據(jù)輸出生成CRC。其界面簡單易用。硬模塊對給定的消息流起著CRC計算器的作用,同時提供一些針對 CRC的參數(shù)作為輸入。CRC的比較功能已經(jīng)超出硬模塊的范圍,應(yīng)集成到FPGA架構(gòu)中。

FPGA 中的每個CRC硬模塊異步計算一個32位校驗和。

圖2是說明硬模塊架構(gòu)的模塊級圖。CRC硬模塊提供一個位反演和字節(jié)反轉(zhuǎn)的輸出。

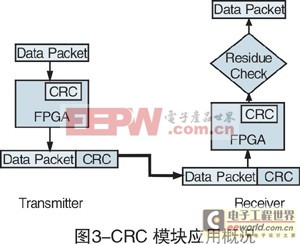

圖3所示為CRC硬模塊的應(yīng)用概況。在發(fā)射器上,CRC經(jīng)計算后附加到給定數(shù)據(jù)包的尾部。在接收器上,對連帶發(fā)射器所附加的CRC一起接收到的整個數(shù)據(jù)包重新計算CRC。

評論