基于FPGA實現VLIW微處理器的設計與實現

超長指令字VLIW(Very Long Instruction Word)微處理器架構采用了先進的清晰并行指令設計[1]。VLIW微處理器的最大優點是簡化了處理器的結構,刪除了處理器內部許多復雜的控制電路[2],它能從應用程序中提取高度并行的指令數據,并把這些機器指令均勻地分配給芯片中的眾多執行單元[3]。本設計是針對VLIW微處理器的基本功能設計實現的,是針對64位指令字和192位數據進行操作處理,主要功能是將指令和數據分別劃分到3個并行操作單元中,在執行單元中根據3個并行指令控制,對3個并行操作單元的數據進行并行處理,同時對操作處理數據進行存儲處理管理。由于篇幅所限,只是將取指令單元、譯碼單元、執行單元、寫回單元和寄存器堆這5個單元的設計方法與設計原理作簡要介紹,沒有給出各個模塊設計仿真波形圖。

1 VLIW微處理器

1.1 VLIW微處理的基本結構

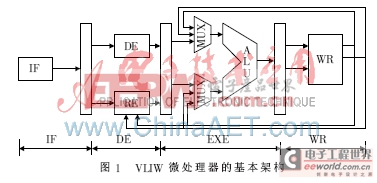

VLIW微處理器的基本架構如圖1所示,采用4級流水線的形式進行架構組織,分別是取指令(IF)、譯碼(DE)、執行(EXE)、寫回(WR)[4]。VLIW微處理器從外部儲存器中,取出指令和數據,指令通過譯碼操作,要求處理器進行執行動作,處理寄存器中的數據或者是取指令單元傳輸來的數據,并通過寫回單元,將處理的數據存儲到寄存器中。取指令單元是從存儲器中取出相對應的指令和數據,并將相應的信息傳輸給譯碼單元和寄存器堆單元;譯碼單元的作用是將取指令單元的指令信息翻譯為執行單元能夠識別的操作,將相應的信息傳輸到執行單元中;執行單元是執行對應的指令信息和處理相關的數據,同時也對寄存器堆送來的數據和指令進行相應的操作;寫回單元是將執行單元的數據存儲到寄存器堆中;寄存器堆是暫時存放取指令單元和寫回單元的數據或是指令。

1.2 VLIW微處理器操作方式

VLIW處理器指令操作方式是實行3種并行的操作,指令格式設置為:最高4位作為保留位,其余各20位依次劃給操作1、操作2、操作3,在每個20位中又分別留有4位的保留位,最后對16位的指令進行劃分為操作碼、源1地址、源2地址、目標地址。3種操作方式是并行執行,相互獨立,互不干擾,并且操作執行都是64位的數據;每一種操作方式都可以實現16種操作運算:空操作、加、減、乘、裝載、移動、讀、比較、或、與非、或非、取反、左移、右移、循環左移、循環右移等操作。任何一種操作都可以對16個寄存器中的數據進行操作處理,且寄存器中所存儲的數據是64位。整個操作過程是將源1與源2寄存器中的數據進行某種操作運算,將其操作處理結果存入目標寄存器中,其操作處理方式是采用寄存器尋址方式。

2 VLIW微處理器的設計與實現

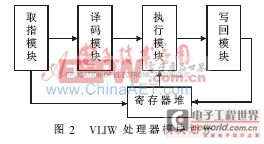

根據VLIW微處理器系統架構和基本原理,將整個VLIW微處理劃分為5個主要部分[5],并對如圖2所示的5個部分進行功能設計與實現。具體原理:取指令模塊把外部存儲器的數據和指令傳送給譯碼模塊,并將部分指令信息傳送給寄存器堆,實現取指令的功能;譯碼模塊將取指模塊的數據和指令進行相對應的譯碼,實現某一種具體的操作,并將譯碼結果傳送到執行模塊中;執行模塊將譯碼模塊或者寄存器堆模塊的數據和指令實現其操作的具體功能,并將操作結果傳送到寫回模塊中;寫回模塊將執行模塊的信息寫入寄存器中,并輸出相關操作處理的數據。

評論