DDR3存儲器接口控制器IP加速數據處理應用

設計和驗證流程

DDR3存儲器控制器IP核必須易于配置、生成并應用到一個目標設計中。使用圖形化用戶界面(GUI)來配置各種DDR3控制器參數是一種簡便的方法,為目標系統快速創建正確的控制器。所有的參數都需要確定,如:存儲器寬度、深度、速度和延遲。每一類配置參數都有其獨立的選項卡,有助于將設計任務分為一個個可管理的“任務塊”。一旦參數選定,生成代碼(用VHDL或Verilog)和生成相應的測試基準應當是比較容易的。

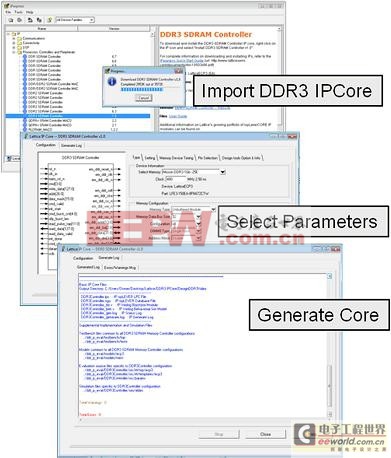

例如,萊迪思IPexpress工具只需三個步驟,如圖3所示,在ispLEVER設計軟件中創建ECP3 DDR3存儲器控制器IP核:

1)從萊迪思網站下載IPexpress工具并將IP核導入。

2)IP核參數可通過每個配置組對應的選項卡進行選擇,配置組有:類型、設置、時序、引腳和設計工具。

3)基于Verilog或VHDL的IP核和測試基準一起生成,包括頂層、監視器、指令生成器、用于Aldec或ModelSim的配置和腳本文件。

圖3:下載、配置和生成IP核設計流程

小結

在數據處理應用的設計中,如本文中視頻處理的例子,當存儲器具有足夠的帶寬時,可以充分利用FPGA的并行處理能力的優勢。DDR3存儲器具有靈活、易于使用的存儲器控制器,如:萊迪思ECP3 DDR3存儲器控制器IP核,加上正確使用突發模式訪問、數據緩沖器分配和存儲器交叉存取可以大大加快數據處理速度。此外,一個經驗證的IP核與可靠的設計和驗證環境也加速了這些應用的上市。

路由器相關文章:路由器工作原理

路由器相關文章:路由器工作原理

存儲器相關文章:存儲器原理

評論