一種基于APA300的創新型FPGA實驗板設計

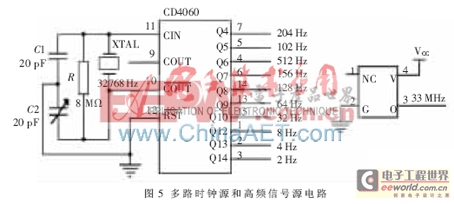

2.4 多路時鐘源和高頻信號源

多路時鐘源和高頻信號源電路原理圖如圖5所示。多路時鐘信號由集成晶體振蕩分頻器CD4060提供,該芯片配以32768Hz的晶體,可產生多路時鐘信號。高頻信號源由33MHz有源晶振提供。

2.5 電源和復位電路

開發板采用三端可調整流穩壓電源LT1085,所以實驗板對電源要求很低,任何交直流電源只要滿足輸出電壓為9 V~12 V,輸出電流不小于500 mA即可使用。APA300內部工作電壓接2.5 V電源,外部IO電壓接3.3 V電源。開發板同時設有復位按鍵電路,復位信號/RESET低電平有效。

2.6 擴展接口

擴展接口為60針的雙列直插接口,外部擴展電路可很方便地與實驗板相連。

3 典型創新性實驗示例

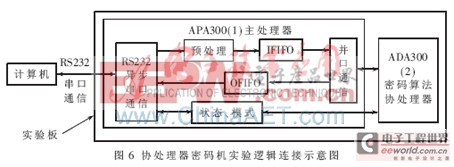

3.1主協處理器實驗:協處理器密碼機

在復雜的系統中,系統處理器不僅要完成整個系統快速、精確的控制,還要處理一些復雜且耗時較長的任務,這勢必會增加處理器的負擔,降低系統性能。為解決這種問題,人們引入了協處理器的概念。將復雜且耗時較長的任務交給一協處理器去處理,協處理器處理完后通知主處理器,從而減輕主處理器的負擔,縮短主處理器的運行周期,同時還能為增強某些功能創造條件。因此協處理器是一種與主處理器協同工作、輔助其完成特定計算任務的專用處理芯片或器件[2]。隨著電子類產品功能的日益增強,運算日趨復雜,復雜的數值處理更加頻繁,協處理器被廣泛應用于消費類產品、工業生產和國防建設。

本實驗板上有2片通過16 bit并行接口互連的APA300,可開展主協處理器實驗。用本實驗板開展協處理器密碼機實驗的邏輯連接示意圖如圖6所示,將連有豐富電路資源的APA300(1)作為主處理器,將APA300(2)作為密碼算法協處理器。主處理器主要負責接口通信、加解密信息的預處理、輸入輸出FIFO的管理、以及加解密狀態、模式的控制。協處理器實現密碼算法,對主處理器通過并行接口送入的數據進行加解密,并把加解密結果回送給主處理器。這樣主協處理器分工合作,完成對計算機數據的加解密,從而可實現協處理器密碼機。

評論