一種以CPLD為核心處理電路的數字電壓表設計

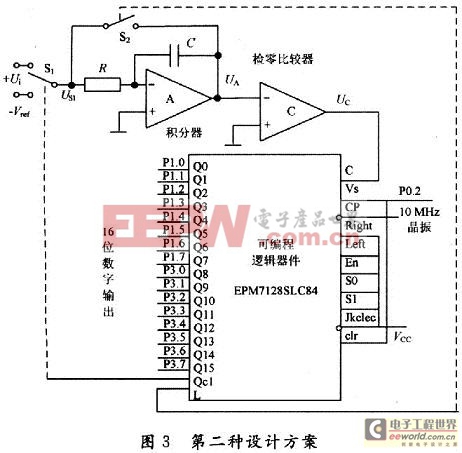

1.2 方案二

采用EDA可編程邏輯器件把16位J-K觸發器組成的計數器和控制電路集成到系統內部,不僅可以消除外界干擾,減小測量誤差,且大大節省空間,提高系統的響應速度。CPLD使用方便、快捷,性價比很高,如圖3所示。

對比兩種方案的性能,本設計選用方案二。

2 系統設計

2.1 硬件部分

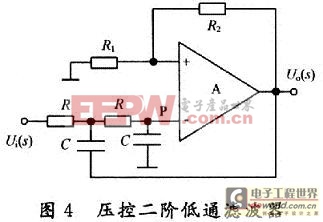

2.1.1 濾波電路

濾波電路采用壓控二階低通濾波器,如圖4所示。運放采用低溫漂高精度運放OP07,取R1=R2=R=1.592 kΩ,C1=C2=10μF,則f0=10 Hz。

傳遞函數為:

![]()

當Aup3時,電路才能正常工作,不產生自激振蕩。令:

![]()

則電壓放大倍數:

![]()

對直流信號的放大倍數為:

![]()

評論