H.264/AVC中CAVLC編碼器的硬件設計實現(xiàn)

(5)寫碼字。

非零系數(shù)級的碼字為“前綴碼字+后綴碼字”,前綴碼字為prefix個0后緊跟一個1(即前綴碼字為1,碼長為prefix+1),后綴碼字值為suffix,碼長為levelsuffixsize。

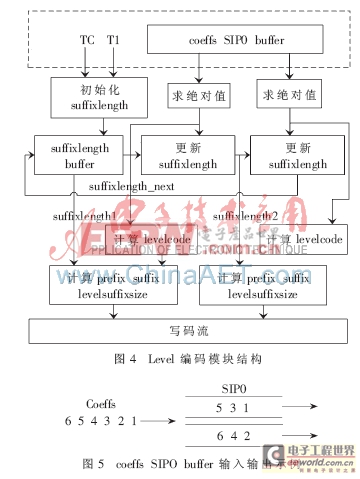

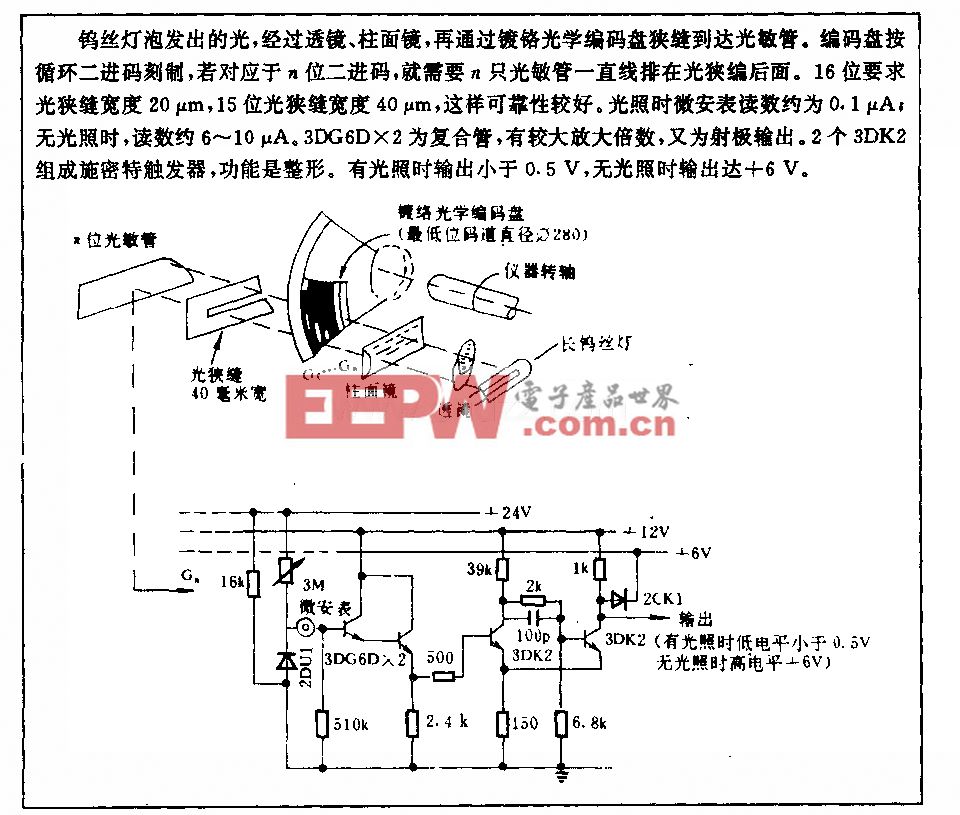

依據(jù)圖3編碼流程,level編碼所需的時鐘周期與TC和T1之差有關,不同的數(shù)據(jù)塊所需的時鐘周期不同,而編碼前需經(jīng)過掃描和統(tǒng)計。當非零系數(shù)較多時,level編碼采用傳統(tǒng)的串行方式所需的時鐘周期可能比統(tǒng)計模塊所耗要多,導致不穩(wěn)定的吞吐量。另一方面,獲得level的碼字需知道該系數(shù)的prefix、suffix以及l(fā)evelsuffixsize,而levelsuffixsize的大小是自適應變化的,與上一個已編碼系數(shù)的絕對值大小有關,這給并行處理帶來了一定困難。為此,采用并行處理和兩級流水線相結合的結構并行處理2個非零系數(shù),如圖4所示。第一級初始化suffixlength,求coeffs的絕對值及中間變量levelcode;第二級更新suffixlength,計算prefix,suffix和levelsuffixlength。模塊coeffs SIPO buffer實現(xiàn)串行輸入并行輸出,輸入輸出關系如圖5所示。

3 實驗驗證分析

Level編碼電路結構采用Verilog HDL語言描述,在ModelSim SE 6.0上進行仿真,使用Synplicity公司的Synplify Pro完成綜合過程。最后采用Xilinx公司VirtexⅡ系列的xc2v250 FPGA進行實現(xiàn)和驗證。

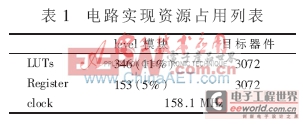

圖6給出了ModelSim的仿真波形,其結果與JVT校驗軟件模型JM16.2[7]的值一致。從圖6可以看出,并行編碼TC-T1個level值比串行方式節(jié)省(TC-T1)/2個時鐘周期,當非零系數(shù)較多時,也能獲得穩(wěn)定的吞吐量。表1給出了Synplify Pro綜合的硬件資源報告。系統(tǒng)允許的最高時鐘頻率為158.1 MHz,硬件資源消耗如表1所示。綜上所述,本設計滿足H.264實時高清視頻編碼的要求。

評論