基于AVR和CPLD的高速數據采集系統的設計

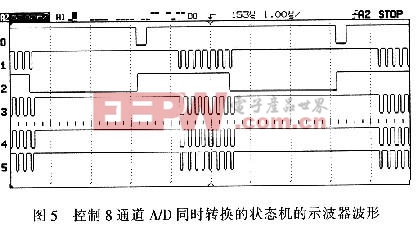

將程序下載至CPLD中運行調試,經過對電路的調試和測量,控制8通道A/D同時轉換的狀態機產生的示波器時序波形如圖5所示,其中,0、1、2、3、4分別對應的是圖3中的CONVST、EOC、EOLC、CS、RD,而第5通道是對FIF0的寫信號。從示波器顯示的波形圖可以看出產生的8個連續的脈沖對應位置完全滿足圖3所要求的時序要求,也就是說在控制器同時控制8路信號的采集時不會出現時序混亂的情況。由此可知,采用本系統中設計的采集程序可以實現同時采集的要求,并且根據采集的脈沖寬度分析可知該系統能滿足采集速度為10 Mb/s的設計要求。

2.2 控制Flash存儲程序設計

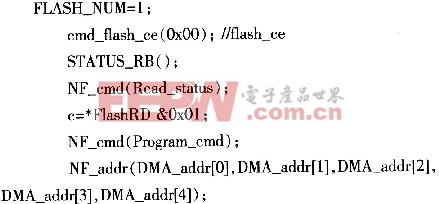

4個Flash存儲器的流水線工作原理如圖2所示,對單獨的每一片Flash來說每一次存儲都是在上一次存儲過程中加載完成后進行,而對于由4片Flash存儲器組成的整個系統,它一直在加載存儲數據,這樣可以保證存儲速度大于采集速度,從而保證存儲過程中不會因單片Flash存儲速度慢而造成丟失數據。實現Flash存儲的主要程序:

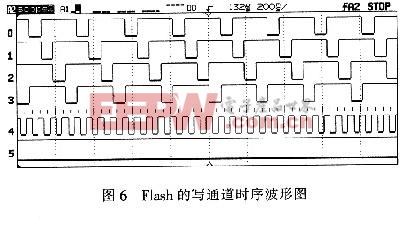

在數據加載期間本系統應采用DMA傳輸控制方式,即:每當FIF0的半滿標志信號HF產生一次有效電平時,ATmegal62就啟動一次中斷,在中斷程序中,ATmegal62將產生NAND Flash命令和有效地址,以及啟動DMA控制器。一旦DMA控制器啟動,ATmegal62就將轉入后臺進行有效地址的運算等,從而參與數據傳輸過程,整個數據從FIFO到Flash存儲器的傳輸過程是由CPLD內部編寫的DMA控制器控制完成。啟動一次DMA控制器傳輸一頁2048個字節的數據,一次中斷完成16 K字節的傳輸。其示波器時序如圖6所示:第0,1,2,3通道是FIF0的讀數據時序波形,第4通道是Flash的寫通道時序波形。

3 結論

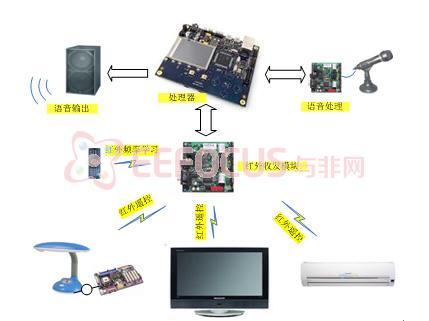

通過使用AVR和CPLD編程,設計實現了一種成本低且可實現10 Mb/s以上并行采集數據率的高速數據采集存儲系統。在分析MAXl308特性及轉換時序的基礎上,設計完成了A/D轉換器及其外圍電路,并通過調試可知時序穩定。通過VHDL語言實現了采集模塊、控制與存儲模塊和Flash存儲功能。在完成硬件連接后調試,試驗結果顯示,該設計能夠實現低成本高速采集,多路同時采集速度大于10 Mb/s采集系統,具有一定的實用價值。

評論