基于AVR和CPLD的高速數據采集系統的設計

2 程序設計與實現

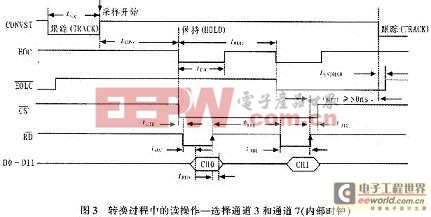

編程實現采集部分的功能,采集部分時序圖如圖3所示。任意選擇兩條通道進行內部時鐘分析,圖中為第3通道和第7通道,當控制信號產生低電平時,控制引腳起作用,觸發采集功能,同時EOC引腳電平至低。在tCTR段時間后讀信號被啟動經過tACC的時間后,12位數據將出現在DO-D11引腳上。在整個采集、存儲過程中其他通道和通道3、通道7一樣,隨后將數據存入數據緩存器中。

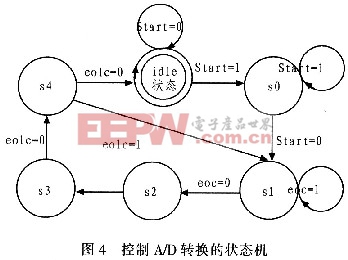

2.1 控制A/D轉換程序設計

根據控制存儲的要求,首先要設計控制A/D轉換的狀態機,用來確定A/D轉換的狀態,根據MAXl308工作時序特點而設計的控制A/D轉換的狀態機轉換圖如圖4所示。實現控制A/D轉換的狀態機部分主要VHDL程序源代碼如下:

評論