基于異步FIFO和PLL的雷達(dá)數(shù)據(jù)采集系統(tǒng)

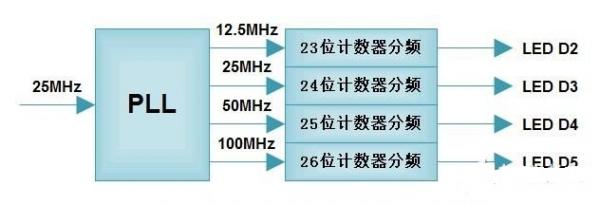

4 基于FPGA的PLL設(shè)計(jì)

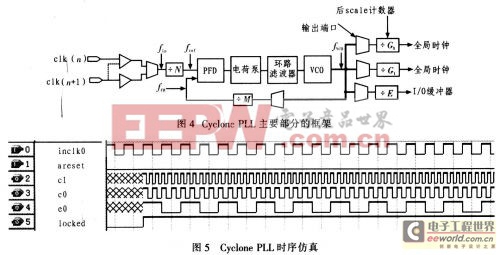

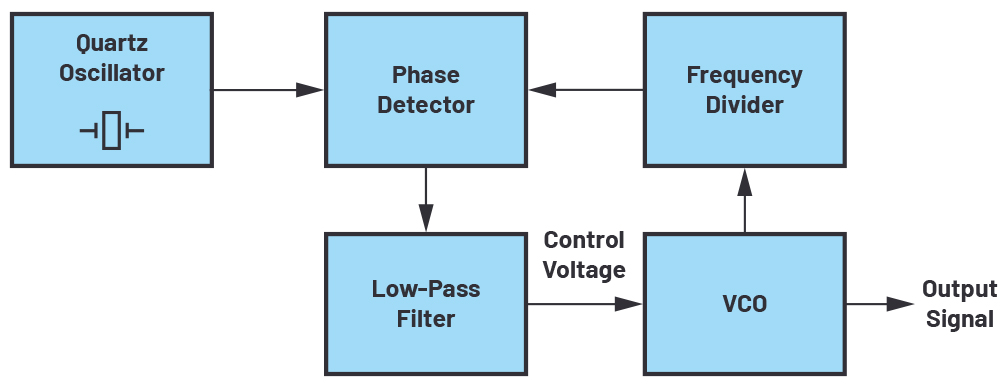

Cyclone FPGA具有鎖相環(huán)(PLL)和全局時(shí)鐘網(wǎng)絡(luò),提供完整的時(shí)鐘管理方案。Cyclone PLL具有時(shí)鐘倍頻和分頻、相位偏移、可編程占空比和外部時(shí)鐘輸出,進(jìn)行系統(tǒng)級(jí)的時(shí)鐘管理和偏移控制。Altera Quattus II軟件無(wú)需任何外部器件,就可啟用Cyclone PLL和相關(guān)功能。PLL常用于同步內(nèi)部器件時(shí)鐘和外部時(shí)鐘,使內(nèi)部工作的時(shí)鐘頻率比外部時(shí)鐘更高,時(shí)鐘延遲和時(shí)鐘偏移最小,減小或調(diào)整時(shí)鐘到輸出(TCO)和建立(TSU)時(shí)間。PLL主要部分的框架如圖4所示。

PLL模塊接收來(lái)自全局時(shí)鐘輸入引腳的時(shí)鐘信號(hào),經(jīng)鎖相環(huán)分/倍頻后作為異步FIFO的讀寫(xiě)時(shí)鐘,也可以作為外部A/D轉(zhuǎn)換器采樣時(shí)鐘。Cyclone PLL中包含一個(gè)前置分頻器N和一個(gè)倍頻器M,設(shè)定范圍為1~32。輸入時(shí)鐘fin經(jīng)預(yù)分頻N后得到參考時(shí)鐘fref:

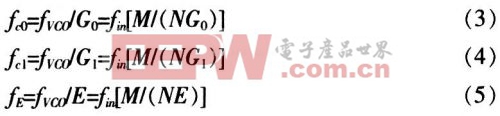

通過(guò)設(shè)置后置分頻器的G0、G1和E值實(shí)現(xiàn)分頻和倍頻。輸出的頻率為:

式中,fc0和fc1是全局時(shí)鐘,為邏輯陣列塊(LAB)提供時(shí)鐘;fE則通過(guò)I/O單元輸出。

圖5為對(duì)PLL模塊仿真結(jié)果。外部晶振輸入高穩(wěn)定時(shí)鐘到inclk0引腳,經(jīng)PLL產(chǎn)生2倍頻時(shí)鐘c0、3倍頻時(shí)鐘cl及經(jīng)分頻的時(shí)鐘e0。

可見(jiàn)使用FPGA內(nèi)部鎖相環(huán)能為高速雷達(dá)數(shù)據(jù)采集系統(tǒng)各部分產(chǎn)生時(shí)鐘源,也使作為高速緩存的雙時(shí)鐘FIF0可應(yīng)用于各種時(shí)鐘域場(chǎng)合。

5 結(jié)論

本文在CycloneⅢFPGA中實(shí)現(xiàn)異步FIFO和鎖相環(huán)(PLL)結(jié)構(gòu)的設(shè)計(jì),避免復(fù)雜的時(shí)鐘管理,簡(jiǎn)化電路設(shè)計(jì),方便采集系統(tǒng)進(jìn)行升級(jí)維護(hù)。高速緩存的設(shè)計(jì)使采集數(shù)據(jù)能的安全地實(shí)現(xiàn)數(shù)據(jù)跨時(shí)鐘域的傳遞,提高了數(shù)據(jù)采集系統(tǒng)的可靠性。

評(píng)論