AES算法中S-box和列混合單元的優化及FPGA實現

3 綜合結果

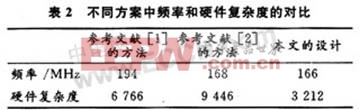

在同等頻率要求的前提下,對S-box及列混合單元進行了優化,目的是減小設計面積。優化后的算法在ModelSimSE 6.2b下進行仿真,并在Xilinx Spartan 3系列FPGA上進行綜合驗證,時鐘頻率達到166 MHz,占用3 212個基本邏輯門(一個基本邏輯門等效于兩輸入/輸出的與門),與參考文獻[1]中方法相比節約52%。由于本文中S-box和InvS-box共用求逆電路,與文獻[2]中的優化方法相比硬件資源節約66%。

其中硬件復雜度為門級電路個數。

4 結 語

在AES的經典算法中S-box常常采用查找表的形式來實現,這樣會占用大量的硬件資源。本文采用S-box與逆S-box組合以及GF(28)到GF(24)同構變換的方法對S-box進行優化,同時,對AES中較復雜的列混合模塊進行了集成優化。優化后的方案在不降低密碼算法安全性的前提下,較好的降低了硬件復雜度,非常適用于信用卡以及其它對硬件規模要求嚴格的應用。

評論