擴展TINI的IO性能

引言

DS80C400評估板包括TINIm400參考電路板和TINIs400插座板,為評估TINI運行環境和利用DS80C400網絡微控制器開發基于TINI的應用提供了一個優秀平臺。TINIm400/TINIs400組合電路板的一個缺點是其通用IO (GPIO)引腳數有限。TINIs400插座板只包含幾個可方便用作GPIO的引腳;插座板上的大多數IO引腳遍布在電路板上,并被用作其它功能(例如,J27為I2C引腳,J4為外部中斷引腳)。

本應用筆記逐步演示了如何使用復雜可編程邏輯器件(CPLD)來配置硬件和開發軟件,從而為TINIs400插座板額外提供32個GPIO引腳。

硬件設置

擴展TINI的IO性能的第一步是在TINIs400插座板上額外安裝四個器件:CPLD、電源調節器,以及兩個插頭。Dallas Semiconductor公司售出的TINIs400插座板上沒有安裝這些器件,但為添加這些器件預留了焊盤和走線。板上并未安裝這些器件,因為許多應用并不需要擴展IO性能,或者采用定制電路板設計。

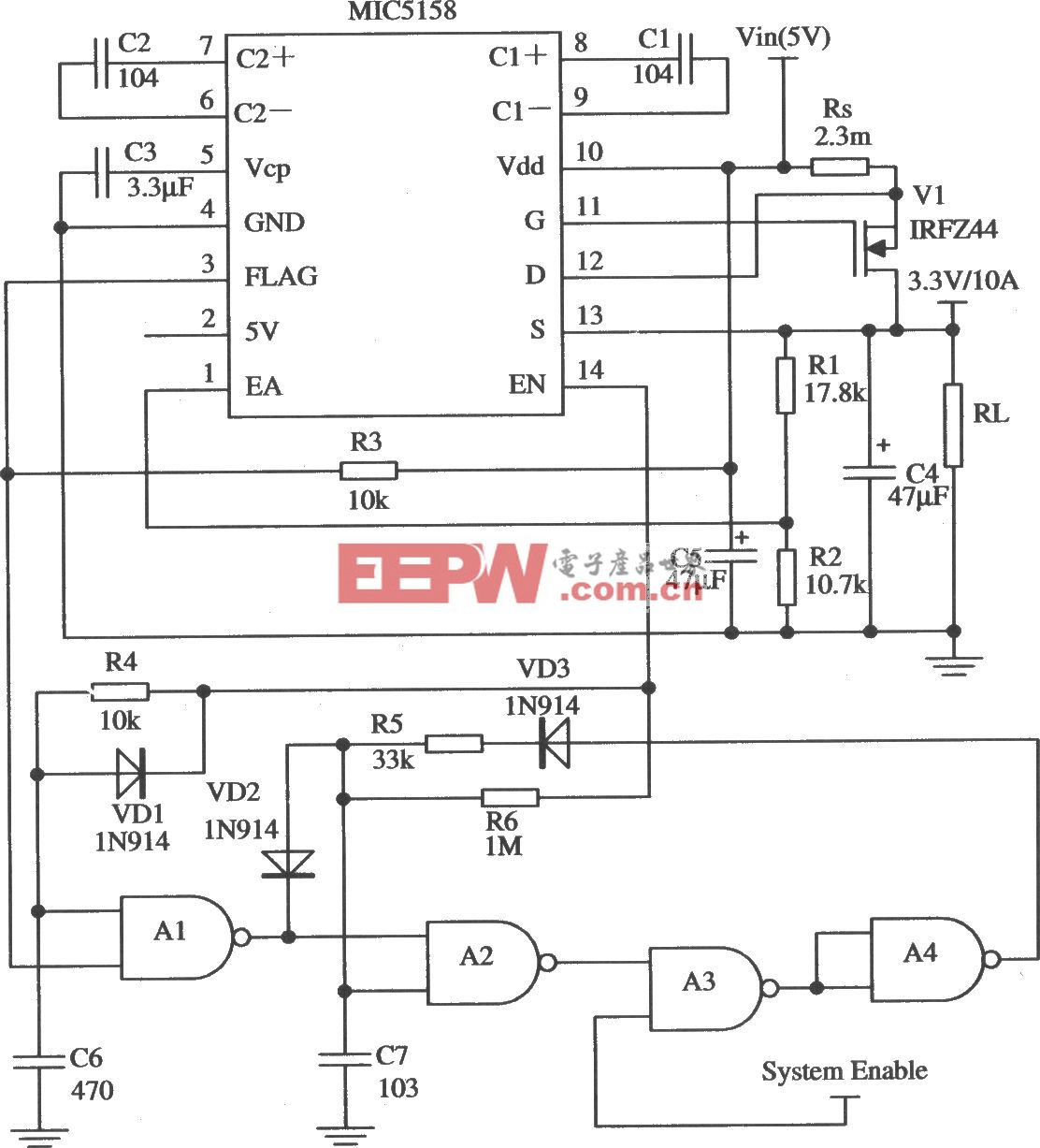

TINIs400電路原理圖1的第7頁詳細給出了擴展TINI IO性能所必需的器件。該電路使用了100引腳VQFP封裝的Xilinx XC2C64 CoolRunner-II CPLD。

XC2C64和更大規模的XC2C128均已在TINI硬件平臺上通過測試,該平臺也支持相同引腳和相同封裝的其他規模的器件。 與CPLD相關的插頭有三個,其中兩個是必需安裝的,具體說明如下:

J30 JTAG編程連接器。通過JTAG接口對XC2C64 CPLD編程。J30連接器為JTAG信號TMS、TCK、TDI和TDO提供引腳。更詳細的討論見下文的CPLD編程一節。

J28擴展IO連接器。通過該連接器可訪問XC2C64器件的32個引腳。對CPLD編程將為這些引腳提供讀/寫接口。

J29額外IO連接器。該連接器提供與XC2C64的16個額外連接,本設計中未用到這些連接器。

除J30和J28插頭以外,還需要安裝以下器件:

U2 MAX1792EUA18調節器

U12 Xilinx CPLD

電容C40至C57。這些電容僅在使用CPLD時才需要,從Dallas Semiconductor獲得的TINIs400插座板應該已安裝了這些電容。如果安裝位置不正確或缺失,在進行其它TINI開發時也許不會注意到。

CPLD配置

CPLD是可編程邏輯器件。可將它看作是可編程硬件,具有非常靈活的內部邏輯,允許通過簡單再編程實現很多功能。用CPLD可以實現32位觸發器,以存儲CPLD輸出引腳的邏輯電平。用Verilog,一種硬件描述語言(HDL)來描述CPLD要實現的功能。Xilinx提供的工具可將Verilog源代碼轉換成二進制形式,用來配置CPLD。

在TINIs400電路板上,XC2C64與TINI微控制器DS80C400的存儲器總線連接。這種連接允許TINI程序通過讀、寫特定地址訪問CPLD。所以,當地址線選擇CPLD時,必須對CPLD編程以正確響應;CPLD必須鎖存寫入的數據總線信號,并且當讀CPLD時必須驅動端口輸入。

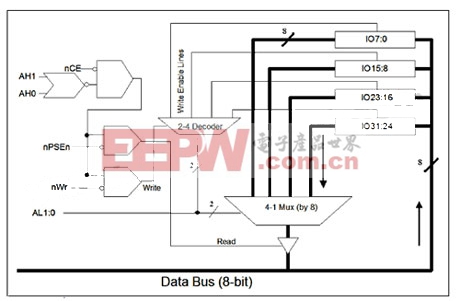

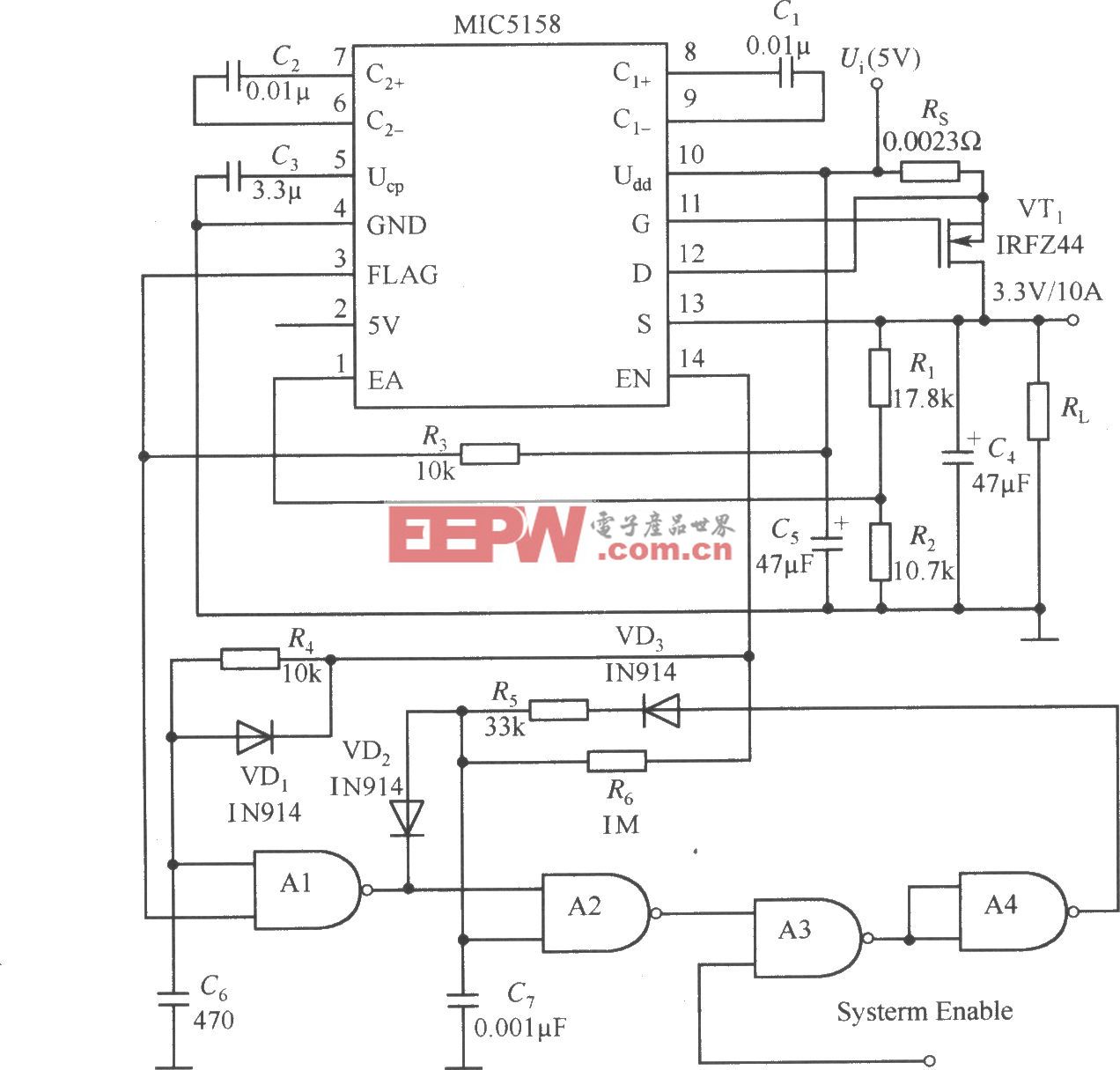

圖1. CPLD功能框圖 |

圖1為CPLD需要實現的功能方框圖。圖中右上部的模塊(IO7:0、IO15:8、IO23:16、IO31:24)代表存儲輸出電平值的觸發器。這些8位寄存器組每一個均連接到數據總線。當通過適當的地址線和寫選通信號(nWr)使能時,數據總線上的內容被鎖存到寄存器內。檢測IO引腳的輸入電平并送入4:1多路復用器,此時低位地址選擇8位值并傳遞到數據總線。如果CPU請求讀(由地址線和nPSEN信號使能),則使能多路復用器的輸出并驅動數據總線。

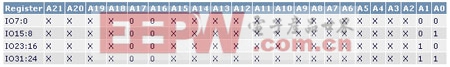

盡管10條地址線(不包括芯片使能)與CPLD連接,但本示例應用只使用其中四條。A17:A16高地址線配合芯片使能6一起使用。當地址位A17:A16為低且nCE6有效(低電平)時,選擇CPLD,但CPLD在讀或寫信號有效之前不起作用。其它兩個地址位A1:A0,用來選擇四個8位寄存器當中的一個作為寫操作的目標地址或讀操作的源地址。這一地址方案意味著許多地址都可使能對四個8位寄存器的訪問。表1概括了這種地址方案的靈活性。

表1. 能夠激活CPLD寄存器的地址線取值

|

由于TINI庫和工作固件將DS80C400配置為每個芯片使能端對應2MB空間,并且DS80C400的地址范圍是24位(16MB),所以八個芯片使能端對應地址的高3位。為激活芯片使能6,24位地址的高3位必須為110b。

盡管表1說明多個地址均可激活寄存器,我們僅使用了以下寄存器地址:

地址C00000h IO7:0

地址C00001h IO15:8

地址C00002h IO23:16

地址C00003h IO31:24

Verilog編碼

有六個Verilog文件用來實現CPLD的32位GPIO功能。本應用筆記的源代碼中包含了這些文件,并附帶提供Xilinx WebPACK(參見下文的討論)工程文件。本工程的Verilog源文件包括:

Buffer8.v:8位緩沖器,用來連接TINI到四個8位寄存器的數據總線。

Mux2x8.v:2:1多路復用器,用來選擇兩條8位總線中的一條。

OneO4e.v:2-4譯碼器,輸出一個取決于低地址位的有效信號。

Reg8OD.v:8位偽開漏極觸發器陣列,用來存儲輸出值。

TSBuffer8.v:8位三態緩沖器,用來驅動數據總線輸入值。

CPLD.v:模塊間的頂層連接。

最應引起注意的Verilog源文件是CPLD.v。它包含輸入、輸出和節點的定義,并且給出在其它文件中定義的實例化模塊。該源文件也是提取寫脈沖和讀脈沖的地方:

assign Reset = ~nRstOut; // make a hi-active Reset

assign IOBank = ~nCE6 ~|AH; // decode the I/O bank

assign ReadT = IOBank ~nPSEn; // qualify Read strobe

assign WriteT = IOBank ~nWr; // qualify Write strobe

然后將信號ReadT作為三態緩沖器的使能信號,使用檢測到的輸入值驅動DS80C400的數據總線:

// Tri-State data bus to TINI needs this buffer

TSBuffer8 U4(ReadT, DataToTINI, D);

信號WriteT送入四個8位寄存器組作為時鐘信號。

// 4 8-bit pseudo-open-drain output drivers

Reg8Out U6(Reset, ~WriteT, Enable[0], DataFromTINI, UIO[ 7: 0]);

Reg8Out U7(Reset, ~WriteT, Enable[1], DataFromTINI, UIO[15: 8]);

Reg8Out U8(Reset, ~WriteT, Enable[2], DataFromTINI, UIO[23:16]);

Reg8Out U9(Reset, ~WriteT, Enable[3], DataFromTINI, UIO[31:24]);

另一個重要的源文件(雖然不是Verilog文件)是CPLD.ucf。該文件給出了CPLD.v中聲明的信號名稱和XC2C64器件實際引腳之間的映射關系。地址線和幾個IO引腳的定義如下:

NET "AL1>" LOC = "P30";

NET "AL0>" LOC = "P32";

NET "AH1>" LOC = "P37";

NET "AH0>" LOC = "P39";

NET "UIO5>" LOC = "P43";

NET "UIO6>" LOC = "P49";

NET "UIO7>" LOC = "P50";

NET "UIO8>" LOC = "P52";

NET "UIO9>" LOC = "P53";

注意,這些引腳定義直接來自TINIs400電路原理圖的第7頁。例如,從電路圖可以看出:地址線3-0 (A[3:0])連接到引腳28、29、30和32。如以上清單所示,我們定義了兩條最低地址線信號(AL1>和AL0>),它們被映射至CPLD的引腳30和32。

CPLD編程

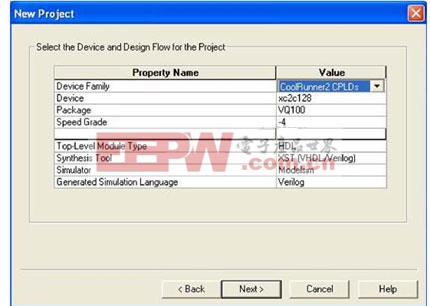

用于CPLD編程的工程文件包含在本應用筆記的源代碼CPLD目錄內。可以使用Xilinx的免費Webpack工具來構建并編程CPLD。本應用筆記中的應用實例是用6.3.03i版本開發的。只要支持CoolRunner 2 CPLD系列,Xilinx工具的最新版本應該也適合本設計。

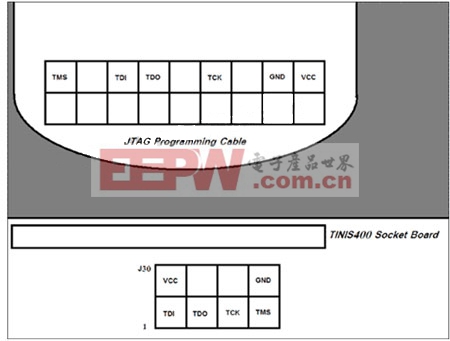

硬件連接

我們使用Avnet Avenue JTAG編程電纜來連接計算機的并口和CPLD的JTAG引腳。許多CPLD或FPGA評估套件均提供JTAG編程電纜。本文使用的編程電纜如圖2所示。

圖2. Avnet Avenue JTAG編程電纜 |

圖3為編程電纜和TINIs400插座板之間所需的連接。對信號做了標記,因此也可以用其他編程電纜。TINIs400插座板要求VCC為3.3V。

圖3. JTAG編程器與TINIS400插座板的連接關系。J30上未標注的引腳沒有連接。 |

載入工程時,點擊File菜單并選擇Open Project。瀏覽本應用筆記的源文件并選擇parallel32.npl。現在已經打開工程并準備構建。接下來說明如何配置一個全新的工程。也可以跳過這一節,直接瀏覽后面的部分了解如何編程CPLD。

遵照以下指導說明,根據應用筆記提供的源代碼創建一個新工程。

在File菜單中選擇New Project。

選擇想要創建新工程的目錄,輸入工程名稱。將創建一個以工程名稱命名的新目錄。確保Top Level Module Type為HDL。點擊Next繼續。

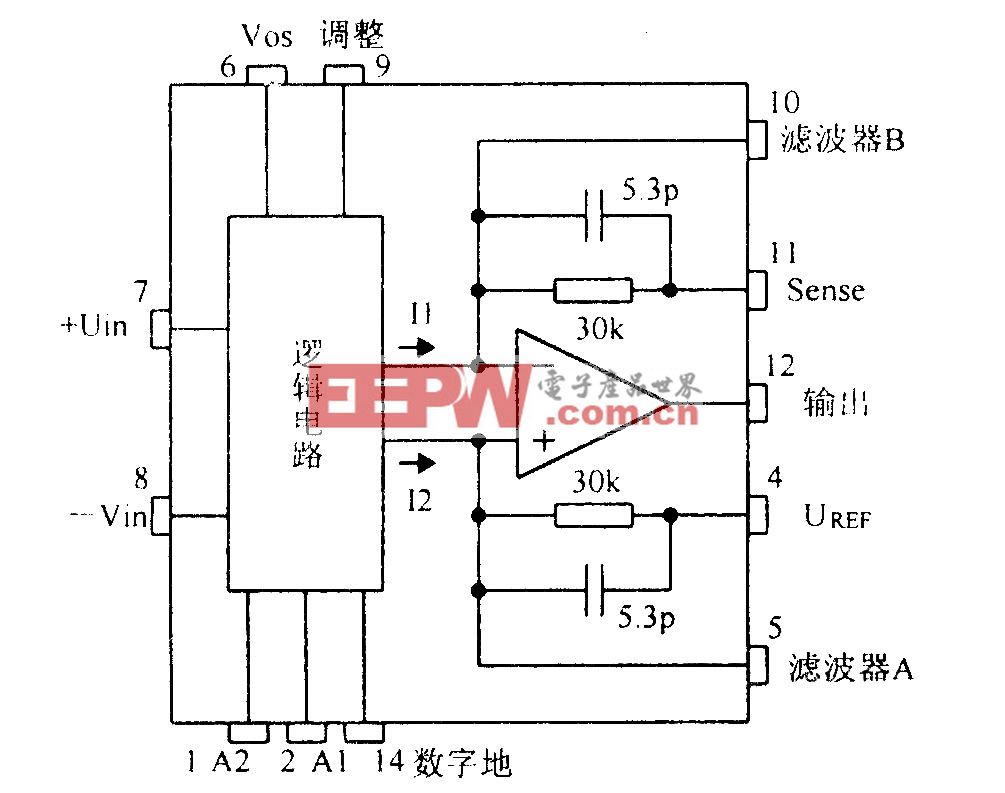

在接下來的菜單中選擇工程需要的器件和封裝。器件系列選擇CoolRunner 2 CPLDs。然后從給出的列表中選擇器件——可以是XC2C64、XC2C128或其它同類器件。封裝選擇VQ100,這是TINIs400插座板認定的封裝。本應用筆記中用到的其它配置選項參見圖4。完成配置后,點擊Next繼續。

圖4. 配置新工程的器件和設計流程 |

下一個窗口詢問新工程中要創建的所有新文件。由于已提供了所有源文件,因此點擊Next,不增加任何新文件。

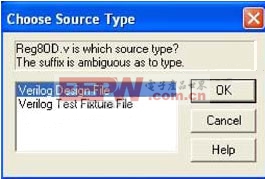

接下來的窗口要求添加任何現有的源文件。點擊Add Source按鈕添加源代碼提供的所有Verilog文件(文件列表見上文的Verilog編碼一節)和CPLD.ucf文件。一旦添加后,程序會詢問:File.v is which source type The suffix is ambiguous as to type (File.v是什么文件類型,后綴類型不明確)。選擇Verilog Design File并點擊OK (參見圖5)。所有輸入文件歸類完畢后,點擊Next繼續。

圖5. 確定輸入源文件的文件類型 |

接下來的窗口概括了新工程的基本信息。查看一遍信息并點擊Finish。

只要在上面第5步中添加了UCF文件,程序將要求把該文件關聯到其影響的內容。在列表中選擇CPLD并點擊OK。

至此,完成了工程創建和配置。現在可以編輯、構建及綜合您的設計。

器件編程

按照以下指導說明來綜合CPLD工程,并對XC2C64器件編程。確保編程電纜已按上文硬件連接一節中說明的方法連接完畢。

CPLD編程:

在Project View (一般在窗口左上部)中選擇Module View標簽。在Module View中選擇主文件CPLD.v。

在Process View窗口(一般在Project View窗口下部)中,展開Implement Design分支并雙擊Generate Programming File。這將運行把Verilog源代碼轉換成二進制文件(用于編程CPLD)需要的所有進程。運行進程時,進程左側將出現說明執行結果的標記。綠勾標志意味著進程成功結束,沒有錯誤或警告。黃色驚嘆號意味著進程成功結束,但有警告信息。紅色X號意味著進程沒有成功結束,出現了錯誤。

一旦程序結束并且成功生成編程文件,雙擊Configure Device (IMPACT)。

將出現一個窗口,顯示Configure Devices。選擇Boundary Scan Mode選項并點擊Next。

在接下來的窗口(Boundary-Scan Mode Selection)中選擇Automatically connect to cable and identify Boundary Scan chain,并點擊Finish。

如果器件連接正確,iMPACT將彈出一個窗口,顯示“There was one device detected in the boundary-scan chain. iMPACT will now direct you to associate a programming or BSDL file with this device....”。點擊OK。

應該在當前的工程目錄下打開一個文件對話窗口(如果沒有在該目錄下打開,應查到其正確位置)。在該窗口中雙擊選擇CPLD.jed。

右鍵單擊Xilinx芯片圖并選擇Program。

確保選中Erase Before Programming and Verify,并且不要選其它項。點擊OK。

此時將出現編程狀態進度條,幾秒鐘(少于20秒)后編程結束,CPLD配置完畢。

進行自己的CPLD功能設計時,當DS80C400不和CPLD通信時,應確保CPLD代碼釋放地址、控制和數據信號為高阻抗狀態。忽略這一點是很常見的錯誤,這會導致奇怪的故障現象,例如電路板會被保持在復位狀態或發生隨機性重啟。發生此類問題時,只要擦除CPLD即可阻止該問題。

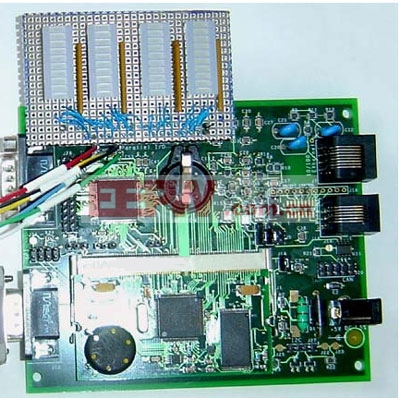

調試電路板

簡單地借助32個LED,即可以演示TINI的IO擴展性能。該演示板用四組LED和四個電阻排來指示每個CPLD IO引腳的狀態。LED板(安裝在TINIs400上)如圖6所示。

圖6. 裝有調試IO板的TINIs400/TINIm400 |

該簡易電路板的原理圖包含在本應用筆記的源代碼中。注意,其中的電阻值是建議值;阻值太高會導致顯示較暗,阻值太低會消耗太多TINI電源電流,并中止執行過程。

軟件接口

這一簡單的存儲器接口實現后,軟件訪問擴展的IO引腳變得相當簡單,將采用匯編語言來實現(作為原生函數嵌入Java應用中)。

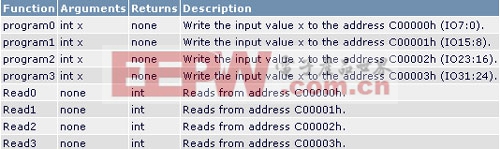

表2給出了為實現接口功能而定義的Java原生函數。

表2. TINI-CPLD接口使用的Java函數

|

注意,也可以用兩個函數完成同樣的工作:program(int address, int x)和read(int address)。但是,在本應用中選擇每個地址分配一個函數,這樣允許應用提取不同的地址作為功能寄存器。每個程序的匯編程序代碼和讀函數都相當簡單。代碼只要求以正確的地址載入數據指針,然后用一個movx指令激活存儲器總線。

Native_program0:

clr a ; request first parameter

lcall NatLib_LoadPrimitive ; load parameter into r3:r0

mov dptr, #0C00000h ; point to memory mapped peripheral

mov a, r0 ; move low byte of source into accumulator

movx @dptr, a ; write to memory mapped peripheral

clr a ; indicate no error condition

ret ;

...

Native_read0:

mov dptr, #0C00000h ; point to memory mapped peripheral

movx a, @dptr ; read from memory mapped peripheral

mov r0, a ; move into low byte of result

clr a ; indicate no error condition

mov r1, a ; unsigned extend to 32-bits

mov r2, a ; unsigned extend to 32-bits

mov r3, a ; unsigned extend to 32-bits

ret ;

應用實例

應用實例在源代碼的javacode文件夾中。該應用向四組LED寫入遞增值。該數值每500ms更新一次,因此可以很方便地知道應用是否正確運行。

由于該應用包括原生函數和Java代碼,因此構建過程比純粹的Java程序更為復雜。源代碼中包含構建批處理文件,但要求針對您開發的系統做一些修改,具體說明如下:

c:worktinitini1.16

ativebinwin32macro -Ic:worktinitini1.16

ativelib cpld.a51

改變目錄以使其指向宏預編譯處理器和本地庫(native library)包含文件在您硬盤上的存儲位置。這些項目是標準TINI SDK的一部分,可從ftp.dalsemi.com/pub/tini/index.html下載。

c:worktinitini1.16

ativebinwin32a390 -f 1.16 -p 400 -l cpld.mpp

改變目錄以使其指向a390匯編程序的地址。它們和宏預編譯處理器存儲在相同的目錄中。

del *.class

從當前目錄中刪除先前存在的類。

javac -bootclasspath C:worktinitini1.16bintiniclasses.jar demo.java

不考慮TINI類文件,構建源文件demo.java。改變目錄以指向TINI的API類,它是TINI SDK的一部分。

java -classpath C:worktinitini1.16bintini.jar;%classpath% TINIConvertor -n cpld.tlib -f . -o demo.tini -d C:worktinitini1.16bintini.db

組合本地庫構建TINI可執行文件,實現與CPLD的接口。Java代碼只需要調用該函數。

System.loadLibrary("cpld.tlib")

為了訪問CPLD的擴展IO引腳,需要再次改變目錄以使其指向TINI SDK附帶的tini.jar工具文件和tini.db類數據庫。

結束語

TINI和CPLD的結合提供了一種簡單接口,可擴展IO性能,并具有高度靈活性。然而,使用可編程邏輯器件時其功能并不僅限于擴展IO。CPLD可用來實現許多邏輯功能和狀態機。與TINI網絡棧、Java虛擬機和操作系統結合使用,CPLD可使TINI系統具有高度可配置性和靈活性。

評論