基于Xilinx FPGA的數字頻域干擾抵消器

五、仿真和測試結果

(1)仿真結果

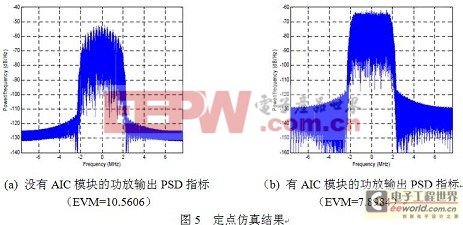

首先,經過功率譜密度圖(PSD)驗證,經過AIC的輸出信號PSD曲線和發送信源PSD曲線基本一致。圖5給出了信干比為-10db時算法的定點仿真結果。

具體而言,在沒有AIC的情況下,輸出信號頻譜主瓣內的波動較大,而且主瓣下降db值減小。采用AIC后,輸出信號頻譜主瓣內的波動基本得以改善,并且下降db值也基本等于原來輸入信源的下降db值,表明AIC性能良好。

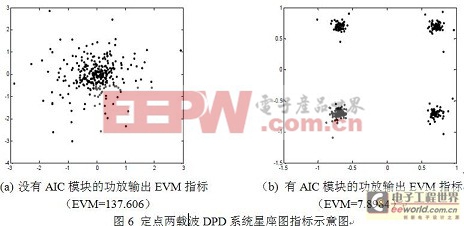

其次,通過量化指標EVM進行比較,圖6給出了信干比為-10db時的EVM指標,可以看出,AIC算法可有效抵消干擾,改善星座圖。

(2)硬件測試說明

在硬件實現時,利用的開發平臺為Virtex II Board.其中V2P30芯片FPGA具有136個硬核乘法器和塊RAM,可滿足自適應濾波算法以及大點數的FFT變換需要大量的乘法器和存儲器的需求。此外,大量的Slice可實現小區搜索模塊以及相關測試平臺的建立。

此外,對于簡易的視頻測試平臺,利用VGA接口完成測試平臺,進行最終的測試驗證。XUP Virtex II PRO板卡帶有高精度的

硬件系統需要實現頻域AIC、小區同步搜索、WCDMA信源發生器、測試平臺4大模塊。其中AIC模塊可劃分為大點數的FFT變換以及相應的串并、并串轉換等主要功能。將設計分為5個大的模塊:頂層模塊,AIC處理模塊,信源發生器,小區搜索以及測試平臺。FFT模塊利用Xilinx公司的IP Core來完成;串并、并串可以利用塊RAM實現;數據處理模塊盡可能地使用SRL16結構來實現,以節省資源。

系統測試按照由部分到整體的思路來完成,首先對各個模塊進行單獨測試,再將部分模塊組合起來完成測試,最后再對整體系統進行測試。這樣,可以將錯誤及早的發現并將其消滅在起步階段。測試主要依靠ChipScope來完成,利用其采集數據,再把數據導入MATLAB中,和定點仿真、ModelSim輸出結果進行比較,完成數據分析,從而確保芯片的運行結果和仿真結果是相同的。在測試中,全部以方波測試平臺為基準。

評論